基于FPGA的动态可重构系统设计与实现

时间:10-08

来源:互联网

点击:

由于数字逻辑系统功能复杂化的需求,单片系统的芯片正朝着超大规模、高密度的方向发展。对于一个大规模的数字系统而言,系统规模是基于各种逻辑功能模块的组合。但是,无论是时序逻辑系统,还是组合逻辑系统,或者组合/时序混合系统,从时间轴上来看,系统中的各个功能模块并不是时刻都在工作,而是根据系统外部的整体要求,轮流或循环地被激活或工作。并且,随着数字逻辑规模的扩大,在相同速度条件下,在一定的时间区间,其功能模块的平均使用率将下降。因此,系统设计应该从传统追求大规模、高密度的方向,转向如何提高资源利用率,用有限的资源实现更大规模的逻辑设计上来。可重构计算技术能够提供硬件的效率和软件的可编程性,它综合了微处理器和ASIC的特点,在空间维和时间维上均可变。

1 可重构技术概述

1.1 可重构的定义

可重构就是在电子系统的工作状态下,动态地改变电路的结构。这主要通过对系统中的可编程逻辑器件进行重新配置或者局部重新配置来完成。利用可重构技术,能在只增加少量硬件资源的情况下,使系统同时具有软件实现和硬件实现的优点。

1.2 可重构方式的分类

按照重构的方式,系统重构可以分为静态系统重构(Static Reconfiguration)和动态系统重构(Dynamic Reconfiguration)。

1.2.1 静态系统重构

静态系统重构是指目标系统的逻辑功能静态重载,只能在运行前配置的系统,如图1所示。

FPGA功能在外部逻辑的控制下,通过存储于存储器中不同的目标系统数据重新下载,从而实现芯片逻辑功能的改变。

1.2.2 动态系统重构

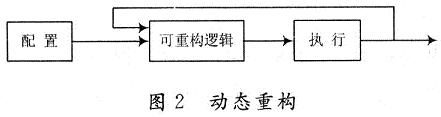

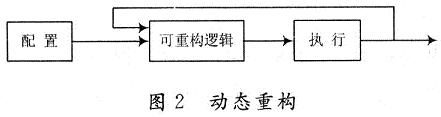

动态系统重构是指能在运行过程中实时配置的可重构系统,如图2所示。

对于时序变化的数字逻辑系统,其时序逻辑的发生不是通过调用芯片内不同区域、不同逻辑资源组合而成的,而是通过对具有专门缓存逻辑资源的FPGA进行局部或全局的芯片逻辑的动态重构而快速实现的。动态系统结构的FPGA具有缓存逻辑(Cache Logic),在外部逻辑的控制下,通过缓存逻辑对芯片逻辑进行全局或局部的快速修改,通过有控制重新布局布线的资源配置来加速实现系统的动态重构。就动态重构实现面积的不同,又可以分为全局重构和局部重构。

(1)全局重构。对FPGA器件或系统能且只能进行全部的重新配置。在配置过程中,计算的中间结果必须取出存放在额外的存储区,直到新的配置功能全部下载完为止,重构前后电路相互独立,没有关联。

(2)局部重构。对重构器件或系统的局部重新配置,与此同时,其余局部的工作状态不受影响。局部重构对减小重构的范围和单元数目,大大缩短重构时间,占有相当的优势。

2 基于FPGA的局部动态可重构技术

2.1 具有局部动态可重构功能的FPGA

过去大家普遍进行动态重构研究的FPGA主要有Xilinx公司的XC6200系列和Atmel公司的AT6000系列等。它们也是基于SRAM结构,但是SRAM的各个单元能够单独访问配置,即局部重构。它们的功能互不影响,因而具有局部重构的特征。这样做的优点显著,但也会付出增大硬件电路规模和功耗的代价。最终要实现电子系统的完全实时重构,应采用结构上具有动态局部重构功能的FPGA器件,如Xilinx公司的Virtex-4系列。

2.2 基于FPGA局部动态可重构技术主要特征及典型原理

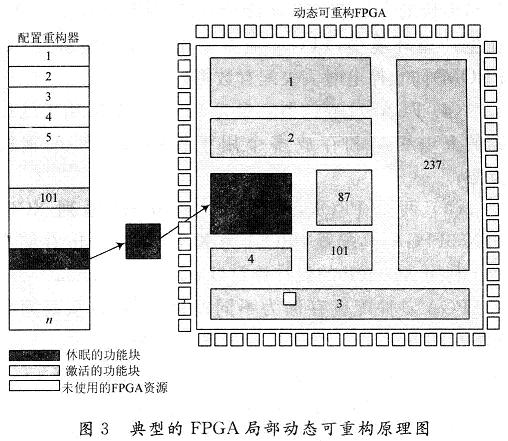

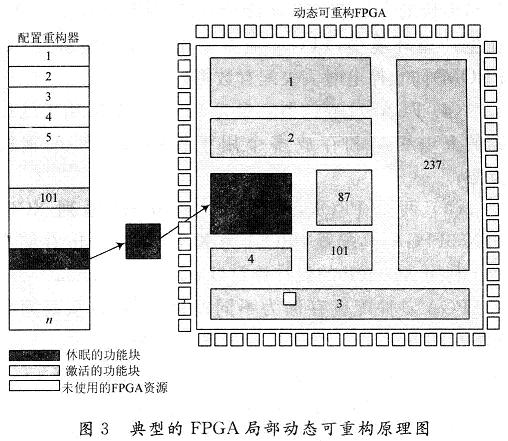

FPGA局部动态可重构技术的特征就是将整体按功能或按时序分解为不同的组合,并根据实际需要,分时对芯片进行局部动态重构,以较少的硬件资源实现较大的时序系统整体功能。图3给出一种典型的FPGA局部动态可重构。由图3可以看出,在外部逻辑的控制下,可以实时动态地对芯片逻辑实现局部重构。通过控制布局、布线的资源,实现系统的动态重构。

2.3 FPGA实现局部动态可重构的结构要求

要使FPGA有效地实现实时系统动态重构,FPGA在结构上必须满足以下要求:

(1)不仅具有可重新编程能力,同时可动态进行系统资源地重新配置,而不会破坏器件中全局或局部逻辑操作能力。很多传统的FPGA把配置数据存放在外部的串行EPROM中。这种方式有3个缺点:重构之前整个FPGA必须停止工作;只是对整个FPGA进行重构;重构时FPGA中以前的内部状态无法保存。新的能够实现动态可重构的FPGA不需要在重构之前触发复位信号,而是将FPGA芯片中的一局部逻辑电路的时钟关闭,然后重新配置逻辑电路,最后恢复时钟信号。

(2)FPGA内部配置信息对称,记载任何时刻,任何通用的基本逻辑功能可以配置于器件的任何一个位置,运用简单模型组合去实现设汁中的复杂功能。

3 基于FPGA的可重构演示系统的设计与实现

3.1 演示验

1 可重构技术概述

1.1 可重构的定义

可重构就是在电子系统的工作状态下,动态地改变电路的结构。这主要通过对系统中的可编程逻辑器件进行重新配置或者局部重新配置来完成。利用可重构技术,能在只增加少量硬件资源的情况下,使系统同时具有软件实现和硬件实现的优点。

1.2 可重构方式的分类

按照重构的方式,系统重构可以分为静态系统重构(Static Reconfiguration)和动态系统重构(Dynamic Reconfiguration)。

1.2.1 静态系统重构

静态系统重构是指目标系统的逻辑功能静态重载,只能在运行前配置的系统,如图1所示。

FPGA功能在外部逻辑的控制下,通过存储于存储器中不同的目标系统数据重新下载,从而实现芯片逻辑功能的改变。

1.2.2 动态系统重构

动态系统重构是指能在运行过程中实时配置的可重构系统,如图2所示。

对于时序变化的数字逻辑系统,其时序逻辑的发生不是通过调用芯片内不同区域、不同逻辑资源组合而成的,而是通过对具有专门缓存逻辑资源的FPGA进行局部或全局的芯片逻辑的动态重构而快速实现的。动态系统结构的FPGA具有缓存逻辑(Cache Logic),在外部逻辑的控制下,通过缓存逻辑对芯片逻辑进行全局或局部的快速修改,通过有控制重新布局布线的资源配置来加速实现系统的动态重构。就动态重构实现面积的不同,又可以分为全局重构和局部重构。

(1)全局重构。对FPGA器件或系统能且只能进行全部的重新配置。在配置过程中,计算的中间结果必须取出存放在额外的存储区,直到新的配置功能全部下载完为止,重构前后电路相互独立,没有关联。

(2)局部重构。对重构器件或系统的局部重新配置,与此同时,其余局部的工作状态不受影响。局部重构对减小重构的范围和单元数目,大大缩短重构时间,占有相当的优势。

2 基于FPGA的局部动态可重构技术

2.1 具有局部动态可重构功能的FPGA

过去大家普遍进行动态重构研究的FPGA主要有Xilinx公司的XC6200系列和Atmel公司的AT6000系列等。它们也是基于SRAM结构,但是SRAM的各个单元能够单独访问配置,即局部重构。它们的功能互不影响,因而具有局部重构的特征。这样做的优点显著,但也会付出增大硬件电路规模和功耗的代价。最终要实现电子系统的完全实时重构,应采用结构上具有动态局部重构功能的FPGA器件,如Xilinx公司的Virtex-4系列。

2.2 基于FPGA局部动态可重构技术主要特征及典型原理

FPGA局部动态可重构技术的特征就是将整体按功能或按时序分解为不同的组合,并根据实际需要,分时对芯片进行局部动态重构,以较少的硬件资源实现较大的时序系统整体功能。图3给出一种典型的FPGA局部动态可重构。由图3可以看出,在外部逻辑的控制下,可以实时动态地对芯片逻辑实现局部重构。通过控制布局、布线的资源,实现系统的动态重构。

2.3 FPGA实现局部动态可重构的结构要求

要使FPGA有效地实现实时系统动态重构,FPGA在结构上必须满足以下要求:

(1)不仅具有可重新编程能力,同时可动态进行系统资源地重新配置,而不会破坏器件中全局或局部逻辑操作能力。很多传统的FPGA把配置数据存放在外部的串行EPROM中。这种方式有3个缺点:重构之前整个FPGA必须停止工作;只是对整个FPGA进行重构;重构时FPGA中以前的内部状态无法保存。新的能够实现动态可重构的FPGA不需要在重构之前触发复位信号,而是将FPGA芯片中的一局部逻辑电路的时钟关闭,然后重新配置逻辑电路,最后恢复时钟信号。

(2)FPGA内部配置信息对称,记载任何时刻,任何通用的基本逻辑功能可以配置于器件的任何一个位置,运用简单模型组合去实现设汁中的复杂功能。

3 基于FPGA的可重构演示系统的设计与实现

3.1 演示验

电子 电路 FPGA Xilinx Atmel ARM 总线 DSP 收发器 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)