用低成本FPGA解决高速存储器接口挑战

时间:10-08

来源:互联网

点击:

DLL校准DQS延时块

源同步接口通常要求调整输入时钟,以便用输入寄存器正确捕获数据。对大多数接口而言,PLL被用于这种调整。然而对于DDR存储器,称为DQS的时钟是受约束的,因此这种方法不可行。在DDR存储器接口,DQS与主时钟的关系会有变化,这是由于PCB上走线的长度和使用的存储器所引起的。

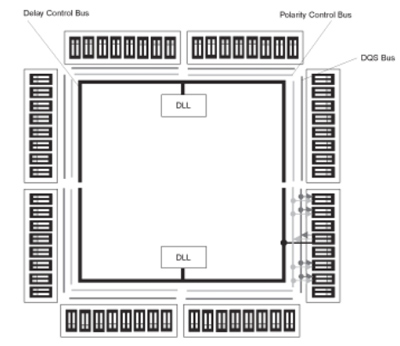

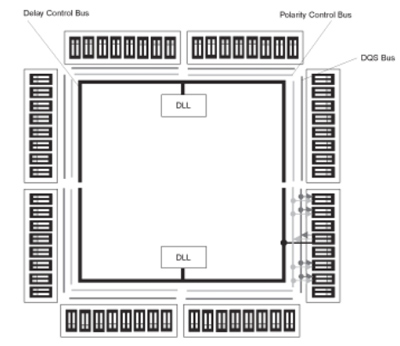

图3:DLL校准总线和DQS/DQS转移分布。

如图2所示,Lattice DQS电路包括一个自动时钟转移电路,用以简化存储器接口设计和保证稳健的操作。此外,DQS延时块还提供用于DDR存储器接口所需的时钟对列。来自焊盘的DQS信号通过DQS延时单元送入专用的布线资源。DQS信号也送入极性控制逻辑,用于控制输入寄存器块中连至同步寄存器的时钟极性。

专用DQS延时块的温度、电压和工艺变化由一组校准信号(6位宽的总线)进行补偿,它们来自器件两侧的两个DLL。每个DLL补偿器件一半的DQS延时,如图3所示。DLL用系统时钟和专用反馈环来补偿。这是一个重要的结构特征,因为这个器件不会受到通常其它FPGA严格的I/O布局要求的牵制。

极性控制逻辑

对于典型的DDR存储器设计,延时DQS选通脉冲和内部系统时钟(在读周期)之间的相位关系是未知的。Lattice-EC器件含有专用电路在这些域间传递数据。为了防止建立和保持时间发生变化,即DQS延时和系统时钟间的域传递,它使用了一个时钟极性选择器,这改变了锁存在输入寄存器块中同步寄存器中的数据的边沿。这需要测定在每个读周期的起始时刻有正确的时钟极性。DDR存储器读操作前, DQS处于三态(由端接上拉)。起始时刻DDR存储器驱动DQS为低电平,一个专用电路用于检测这个传递,这个信号用来控制至同步寄存器的时钟极性。

源同步接口通常要求调整输入时钟,以便用输入寄存器正确捕获数据。对大多数接口而言,PLL被用于这种调整。然而对于DDR存储器,称为DQS的时钟是受约束的,因此这种方法不可行。在DDR存储器接口,DQS与主时钟的关系会有变化,这是由于PCB上走线的长度和使用的存储器所引起的。

图3:DLL校准总线和DQS/DQS转移分布。

如图2所示,Lattice DQS电路包括一个自动时钟转移电路,用以简化存储器接口设计和保证稳健的操作。此外,DQS延时块还提供用于DDR存储器接口所需的时钟对列。来自焊盘的DQS信号通过DQS延时单元送入专用的布线资源。DQS信号也送入极性控制逻辑,用于控制输入寄存器块中连至同步寄存器的时钟极性。

专用DQS延时块的温度、电压和工艺变化由一组校准信号(6位宽的总线)进行补偿,它们来自器件两侧的两个DLL。每个DLL补偿器件一半的DQS延时,如图3所示。DLL用系统时钟和专用反馈环来补偿。这是一个重要的结构特征,因为这个器件不会受到通常其它FPGA严格的I/O布局要求的牵制。

极性控制逻辑

对于典型的DDR存储器设计,延时DQS选通脉冲和内部系统时钟(在读周期)之间的相位关系是未知的。Lattice-EC器件含有专用电路在这些域间传递数据。为了防止建立和保持时间发生变化,即DQS延时和系统时钟间的域传递,它使用了一个时钟极性选择器,这改变了锁存在输入寄存器块中同步寄存器中的数据的边沿。这需要测定在每个读周期的起始时刻有正确的时钟极性。DDR存储器读操作前, DQS处于三态(由端接上拉)。起始时刻DDR存储器驱动DQS为低电平,一个专用电路用于检测这个传递,这个信号用来控制至同步寄存器的时钟极性。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)