Quartus II 调用ModelSim 仿真

时间:10-09

来源:互联网

点击:

下面是基于在Altera Quartus II 下如何调用ModelSim 进行仿真的一个实例。

不能否认,Quartus II(我用的7.0)无法像ISE 那样方便的直接调用ModelSim,而是需要额外的做一些工作。这确实给我们的仿真调试带来了一些不便。特权同学也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让大家少走一些弯路。

1、 打开Quartus II,新建一个工程,工程代码如下(只是做一个简单的二分频电路):

module modelsim_test(

clk,rst_n,div

);

input clk; //系统时钟

input rst_n; //复位信号,低有效

output div; //2 分频信号

reg div;

always @ (posedge clk or negedge rst_n)

if(!rst_n) div <= 1'b0;

else div <= ~div;

endmodule

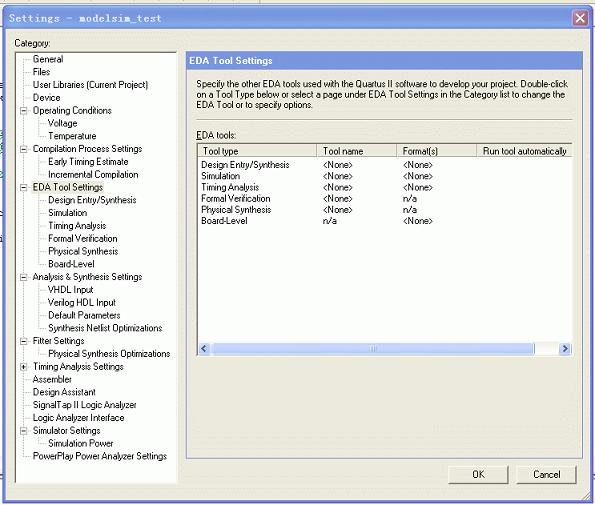

2、 进入菜单栏的Assignments EDA Tool Settings,进入如下界面:

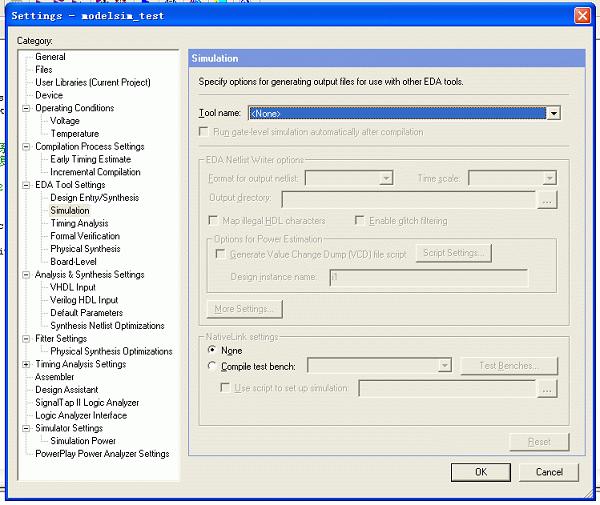

双击“EDA tools”下的“Simulation”选项,弹出如下界面:

3、 以上设置完成,重新编译工程。

打开工程目录,看到多了一个“simulation”文件夹,再打开该文件夹下的“modelsim”文件夹。看到有三个文件,其中.vo 文件就是我们的代码布局布线信息。仿真还需要几个文件,我们把它们都拷贝到该目录下。

4、 打开“C:altera70quartusedasim_lib”(具体quartus 软件安装文件的根目录视您的实际情况而定,大体路径都一样),因为我们用的是MAX II器件,所以把“maxii_atoms.v”拷贝到3 中提到的目录下,这个文件是仿真元件库。

5、 编写一个工程RTL 源码的Testbench 文件,用于作为仿真激励(具体如何编写清参考相关数据文档资料)。这个实例的testbench 如下:

module vtf_test;

// Inputs

reg clk;

reg rst_n;

// Output

wire div;

modelsim_test u1(

.clk(clk),

.rst_n(rst_n),

.div(div)

);

initial begin

clk = 0;

forever

#10 clk = ~clk; //产生50MHz 的时钟

end

initial begin

rst_n = 0;

#1000 rst_n = 1; //上电后1us 复位信号

#1000;

$stop;

end

endmodule

将该文件命名为tb_test.v,保存到3 提到的文件夹下。

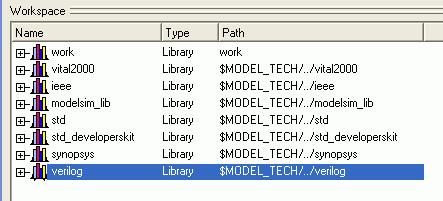

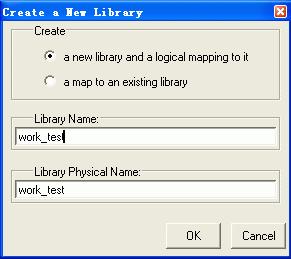

6、 在wokspace 的library 面板的空白处单击右键,选择“new”→“library”

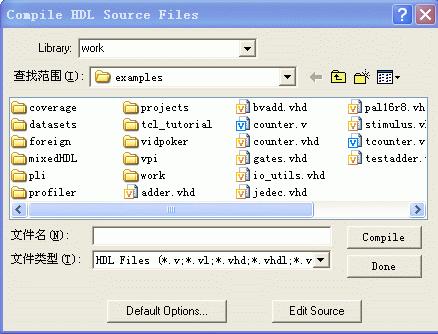

7、 启动ModelSim 软件,点击菜单栏的Compile􀃆compile 命令,弹出如下界面:

Library 选择刚才新建的“work_test”,查找范围定位到我们3 提到的文件夹下。全选在该目录下可以看到的文件,点击Compile(注意该文件夹必须在全英文/数字路径下,否则会出错无法编译)。

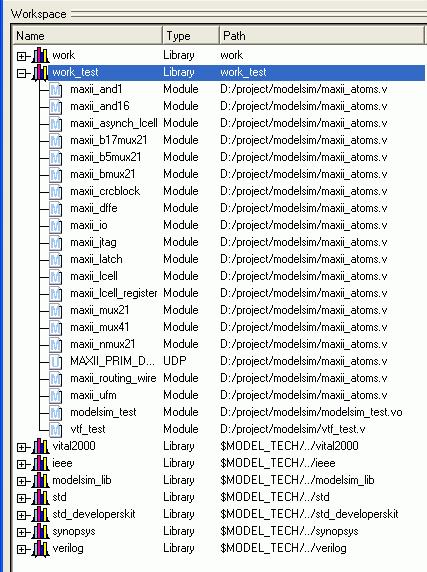

8、 我们回到wokspace 的library 面板,work_test 多处了下拉框,点击后如下:

9、 执行上面的操作后,软件自动弹出wokspace 的sim 面板如下:

在vtf_test 栏单击右键,在弹出菜单中选择Add􀃆Add to Wave。然后软件将弹出波形窗口。

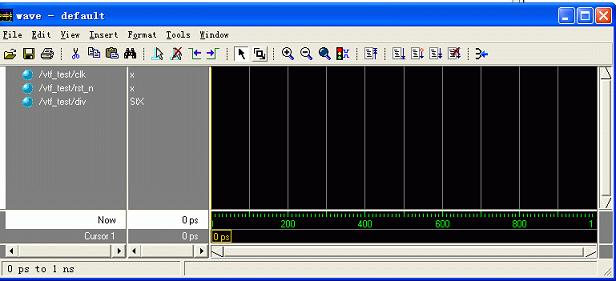

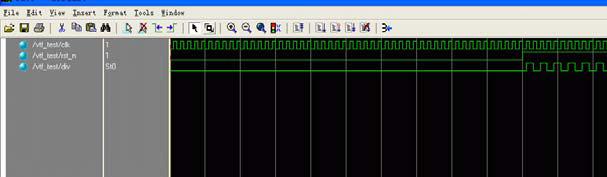

10、 波形窗口如下:

这时我们点击全速编译(一次不行,多点一次,工具栏倒数第三个按钮),

然后点击观看全部波形(放大缩小按钮后面一个蓝色按钮)。

11、 仿真结果如下:

可以看到div 信号确实是clk 的二分频。呵呵,基本的操作就到此结束了。

不能否认,Quartus II(我用的7.0)无法像ISE 那样方便的直接调用ModelSim,而是需要额外的做一些工作。这确实给我们的仿真调试带来了一些不便。特权同学也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让大家少走一些弯路。

1、 打开Quartus II,新建一个工程,工程代码如下(只是做一个简单的二分频电路):

module modelsim_test(

clk,rst_n,div

);

input clk; //系统时钟

input rst_n; //复位信号,低有效

output div; //2 分频信号

reg div;

always @ (posedge clk or negedge rst_n)

if(!rst_n) div <= 1'b0;

else div <= ~div;

endmodule

2、 进入菜单栏的Assignments EDA Tool Settings,进入如下界面:

双击“EDA tools”下的“Simulation”选项,弹出如下界面:

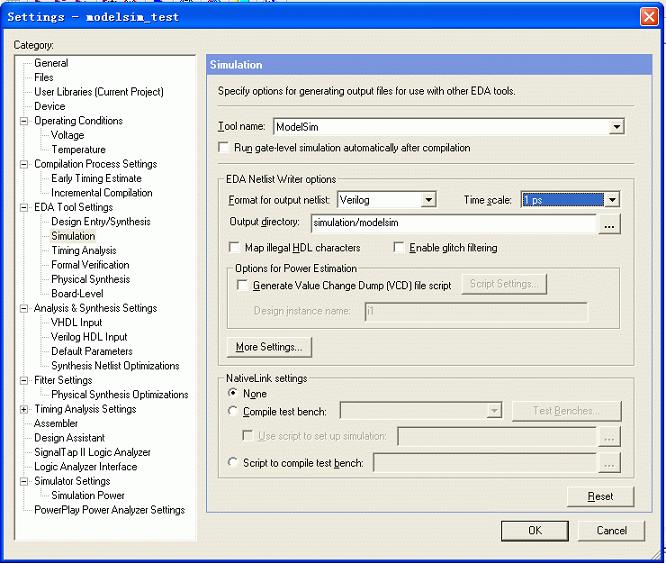

点击Tool name 最右侧的下拉条,选择“ModelSim”,在弹出的界面做如下设置:

3、 以上设置完成,重新编译工程。

打开工程目录,看到多了一个“simulation”文件夹,再打开该文件夹下的“modelsim”文件夹。看到有三个文件,其中.vo 文件就是我们的代码布局布线信息。仿真还需要几个文件,我们把它们都拷贝到该目录下。

4、 打开“C:altera70quartusedasim_lib”(具体quartus 软件安装文件的根目录视您的实际情况而定,大体路径都一样),因为我们用的是MAX II器件,所以把“maxii_atoms.v”拷贝到3 中提到的目录下,这个文件是仿真元件库。

5、 编写一个工程RTL 源码的Testbench 文件,用于作为仿真激励(具体如何编写清参考相关数据文档资料)。这个实例的testbench 如下:

module vtf_test;

// Inputs

reg clk;

reg rst_n;

// Output

wire div;

modelsim_test u1(

.clk(clk),

.rst_n(rst_n),

.div(div)

);

initial begin

clk = 0;

forever

#10 clk = ~clk; //产生50MHz 的时钟

end

initial begin

rst_n = 0;

#1000 rst_n = 1; //上电后1us 复位信号

#1000;

$stop;

end

endmodule

将该文件命名为tb_test.v,保存到3 提到的文件夹下。

6、 在wokspace 的library 面板的空白处单击右键,选择“new”→“library”

在新弹出界面中做如下设置,然后点击“OK”。

7、 启动ModelSim 软件,点击菜单栏的Compile􀃆compile 命令,弹出如下界面:

Library 选择刚才新建的“work_test”,查找范围定位到我们3 提到的文件夹下。全选在该目录下可以看到的文件,点击Compile(注意该文件夹必须在全英文/数字路径下,否则会出错无法编译)。

8、 我们回到wokspace 的library 面板,work_test 多处了下拉框,点击后如下:

我们右键单击vtf_test 文件,在弹出的菜单中选择Simulation

9、 执行上面的操作后,软件自动弹出wokspace 的sim 面板如下:

在vtf_test 栏单击右键,在弹出菜单中选择Add􀃆Add to Wave。然后软件将弹出波形窗口。

10、 波形窗口如下:

这时我们点击全速编译(一次不行,多点一次,工具栏倒数第三个按钮),

然后点击观看全部波形(放大缩小按钮后面一个蓝色按钮)。

11、 仿真结果如下:

可以看到div 信号确实是clk 的二分频。呵呵,基本的操作就到此结束了。

Altera Quartus ModelSim 仿真 电路 EDA 相关文章:

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 智能命令行设计及其在 SOPC 系统中的应用(08-14)

- 我的FPGA学习历程(05-23)

- 在FPGA中实现源同步LVDS接收正确字对齐(05-01)

- Altera FPGA下载配置(11-11)