FPGA实现无线电信设备的低延迟变化CPRI

时间:10-06

来源:互联网

点击:

无线电信设备制造商正受到以更小体积、更低功耗、更低制造成本来布署基站架构的压力。当通过WiMAX和LTE网络开展新业务的同服务时,他们还面临提高覆盖范围、带宽和可扩展性的压力。解决这些应用挑战的关键策略是从基站中分离出RF接收器和功率放大器,并紧靠它们各自的天线重新设计,从而使简化后的基站直接驱动天线。本文讨论利用带嵌入式SERDES收发器和CPRI链路IP内核的低成本FPGA,来实现电信系统低延迟变化设计的考虑因素。

无线电信设备制造商正受到以更小体积、更低功耗、更低制造成本来布署基站架构的压力。当通过WiMax和LTE网络开展新业务的同服务时,他们还面临提高覆盖范围、带宽和可扩展性的压力。解决这些应用挑战的关键策略是从基站中分离出RF接收器和功率放大器,并紧靠它们各自的天线重新设计,从而使简化后的基站直接驱动天线。本文讨论利用带嵌入式SERDES收发器和CPRI链路IP内核的低成本FPGA,来实现电信系统低延迟变化设计的考虑因素。

实现这种系统的一个解决方法是利用通用公共无线接口(CPRI),通过光纤传送数字基带数据到远程无线头(RRH)。根据CPRI规范,基站用作无线设备控制器(REC),而RRH用作无线设备(RE)。在此方案中,所有的RE在指定的时间必须同步和传输,这样,待解决的器件和系统级关键问题是如何使各种天线之间的传输时间变化最小。本文讨论利用带嵌入式SERDES收发器和CPRI链路IP内核的低成本FPGA,来实现电信系统低延迟变化设计的考虑因素。

RRH的部署

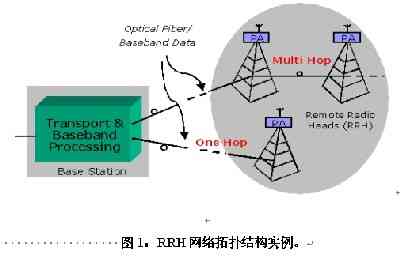

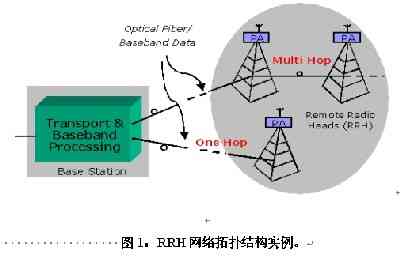

从驻点(hotel)基站分离无线频率(RF)收发器和功率放大器的优点很多,如图1所示。但最吸引人的优势体现在功耗、部署的灵活性、更小的固定面积,以及更低的CAPEX(固定投资)和OPEX(运营费用)方面。

由于无线头从主基带模块里分离出来,所以必须确保系统能校准无线头和hotel BTS之间的所有延时,以便能遵从传输时间规范(即最大可接受的周期内对齐)。由于采用分集传输,公共数据经由不同的RE传送,这意味着发送对齐误差在各种RE之间是可知且可控,以取保正确运行。

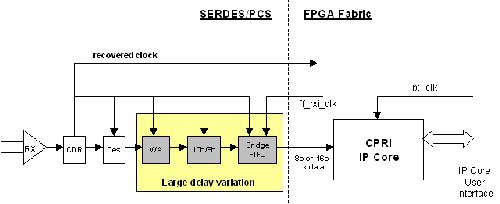

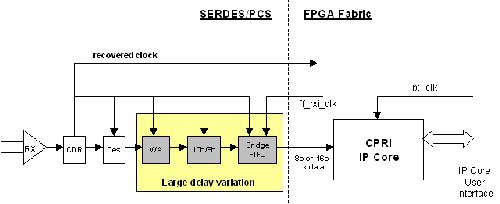

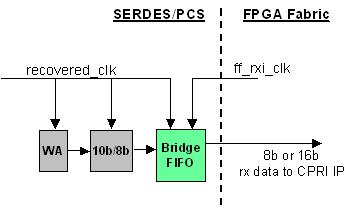

通常,通过基于FPGA的CPRI链接的回路延迟取决于其发送路径(包括串行器、物理编码子层,桥接FIFO和FPGA结构),和返回时的接收路径(类似于发送路径,不过是反向的)。图2给出了一个例子。此外,这个延时需要再加上传输媒质(最常用的是光纤)导致的延时。

因为操作员将延时信息用于系统校准,比如为了使信号强度最大和改进跟踪需要确定不同系统的地理位置,这必须确保通过整个来回路径的延时变化在系统正常工作期间以及各种上电方案和情况时随工艺、电压和温度变化最小。因为从每个RRH跳的变化是累加的,这个需求通过级联RRH被放大,在延时变化规范方面导致甚至更小的容忍度。

CPRI规范对此特别关注,针对CPRI收发器的单向和来回行程延时,在3.5.3(R-19和R-20)条款做了清楚的说明。对于3GPP和WiMAX,这个规范为一跳的延时精确性是±16.276ns(来回行程,不包括传输媒质),每增加一跳,减少这个数目(即2跳是±16.276除2,或者±8.138ns等)。

针对低延迟变化的FPGA实现

图2给出了传统SERDES/PCS实现中的主要功能块,黄色部分是导致延时变化的主要功能块。

图2:传统的CPRI接收器实现方案。

导致延时变化的模块有好几个,包括模拟SERDES、数字PCS逻辑以及实际的软IP。模拟SERDES有相对紧凑的时序,百万分之一秒的变化主要源于工艺、电压和温度的变化。因此对延时变化预算没有很大的影响。

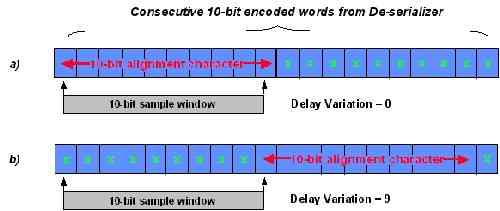

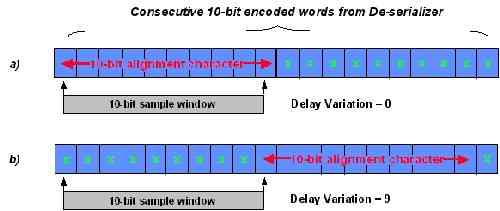

然而,字对齐和桥接FIFO是引起延时变化很大的两个主要原因。如图3所示,字对齐功能会导致多达9位周期的延时变化,这取决于10位周期内字对齐指针的初始位置。如果10位的采样窗口能很好地捕获对齐字符(如图3a所示),那就没有延时。如果采样窗口没有与字符对齐,则将导致多达9位周期的延时(如图3b所示)。对于工作频率为2.488Gbps(400ps周期)的CPRI链路,这意味最坏延迟变化为±1.8ns。

图3:字对齐导致的延时变化。

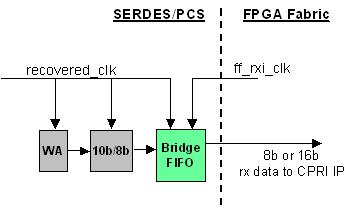

采用基于SERDES的FPGA混合结构,还需要桥接FIFO来支持从高速PCS时钟到FPGA时钟域的转换。通过设计,这个FIFO可导致多达2个并行时钟周期的延时变化。在2.488Gbps的线速下,PCS并行时钟以该速率的十分之一运行,时钟周期大约为4ns。因此,FIFO(Tx&Rx)的每个方向上都有±8ns的最大延迟变化,这导致一共±16ns的延迟变化。

使情况变得更糟糕的是设计者没有预见到这些延时变化。因此不能在系统级估计和补偿这些变化,在支持诸如分集传输和GPS服务时,这是主要的问题。

图4:桥接FIFO导致的延时变化。

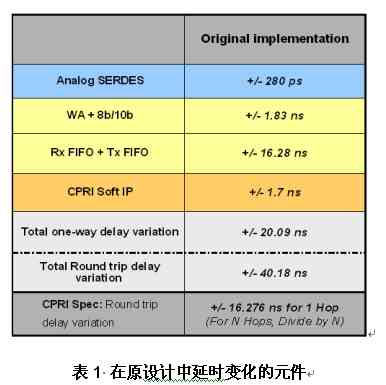

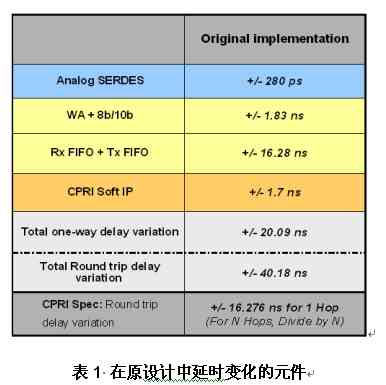

针对基于FPGA的传统嵌入式SERDES/PCS,表1总结了导致整个执行时间发生的主要因素,并与CPRI规范进行了比较。分析这些数目,可很清楚看到字对齐和桥接FIFO对大的延时变化起主要作用,导致超过规范的来回行程延时容忍度。

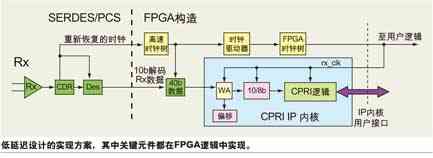

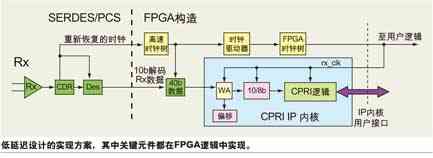

幸运的是,通过对传统的实现做一些小的修改就可以解决这个问题。用户可以绕过嵌入式数字PCS功能,在FPGA中实现这些逻辑。因为现在的逻辑运行在单个FPGA时钟域中,所以这个方法不再需要桥接FIFO,并且设计者可以访问导致延时的字对齐电路。在FPGA逻辑里可以通过访问寄存器的方式来获得字对齐电路测量到的延迟信息,而从在系统级针对延时变化进行补偿。这些补偿允许无线头之间在指定的窗口内进行传输以支持前面提到的业务,诸如分集传输和GPS。图5给出了低延迟设计的实现方案,关键元件都在FPGA逻辑中实现。

如果采用这个推荐的实现方案,则不再需要导致大的延时变化的单元,即省去了桥接FIFO。可访问字对齐电路的寄存器使用户能计算并进行系统级补偿,以确保不同无线头的传输都在规定的时序窗内进行。当然,模拟SERDES和CPRI IP,或者设计本身仍然存在延时,但此时整个配置的精确度已得到大大改善,可以在多跳应用中使用。该方案占用的器件资源很小,新的模块只需几百个LUT。表2列出了这个配置中新的延时变化。可以看到总的延时变化大大下降。对单跳来说这很容易满足来回行程延时规范,对支持多达4级的多跳应用是足够的低。

图5:低延迟设计的实现方案,其中关键元件都在FPGA逻辑中实现。

无线电信设备制造商正受到以更小体积、更低功耗、更低制造成本来布署基站架构的压力。当通过WiMax和LTE网络开展新业务的同服务时,他们还面临提高覆盖范围、带宽和可扩展性的压力。解决这些应用挑战的关键策略是从基站中分离出RF接收器和功率放大器,并紧靠它们各自的天线重新设计,从而使简化后的基站直接驱动天线。本文讨论利用带嵌入式SERDES收发器和CPRI链路IP内核的低成本FPGA,来实现电信系统低延迟变化设计的考虑因素。

实现这种系统的一个解决方法是利用通用公共无线接口(CPRI),通过光纤传送数字基带数据到远程无线头(RRH)。根据CPRI规范,基站用作无线设备控制器(REC),而RRH用作无线设备(RE)。在此方案中,所有的RE在指定的时间必须同步和传输,这样,待解决的器件和系统级关键问题是如何使各种天线之间的传输时间变化最小。本文讨论利用带嵌入式SERDES收发器和CPRI链路IP内核的低成本FPGA,来实现电信系统低延迟变化设计的考虑因素。

RRH的部署

从驻点(hotel)基站分离无线频率(RF)收发器和功率放大器的优点很多,如图1所示。但最吸引人的优势体现在功耗、部署的灵活性、更小的固定面积,以及更低的CAPEX(固定投资)和OPEX(运营费用)方面。

由于无线头从主基带模块里分离出来,所以必须确保系统能校准无线头和hotel BTS之间的所有延时,以便能遵从传输时间规范(即最大可接受的周期内对齐)。由于采用分集传输,公共数据经由不同的RE传送,这意味着发送对齐误差在各种RE之间是可知且可控,以取保正确运行。

通常,通过基于FPGA的CPRI链接的回路延迟取决于其发送路径(包括串行器、物理编码子层,桥接FIFO和FPGA结构),和返回时的接收路径(类似于发送路径,不过是反向的)。图2给出了一个例子。此外,这个延时需要再加上传输媒质(最常用的是光纤)导致的延时。

因为操作员将延时信息用于系统校准,比如为了使信号强度最大和改进跟踪需要确定不同系统的地理位置,这必须确保通过整个来回路径的延时变化在系统正常工作期间以及各种上电方案和情况时随工艺、电压和温度变化最小。因为从每个RRH跳的变化是累加的,这个需求通过级联RRH被放大,在延时变化规范方面导致甚至更小的容忍度。

CPRI规范对此特别关注,针对CPRI收发器的单向和来回行程延时,在3.5.3(R-19和R-20)条款做了清楚的说明。对于3GPP和WiMAX,这个规范为一跳的延时精确性是±16.276ns(来回行程,不包括传输媒质),每增加一跳,减少这个数目(即2跳是±16.276除2,或者±8.138ns等)。

针对低延迟变化的FPGA实现

图2给出了传统SERDES/PCS实现中的主要功能块,黄色部分是导致延时变化的主要功能块。

图2:传统的CPRI接收器实现方案。

导致延时变化的模块有好几个,包括模拟SERDES、数字PCS逻辑以及实际的软IP。模拟SERDES有相对紧凑的时序,百万分之一秒的变化主要源于工艺、电压和温度的变化。因此对延时变化预算没有很大的影响。

然而,字对齐和桥接FIFO是引起延时变化很大的两个主要原因。如图3所示,字对齐功能会导致多达9位周期的延时变化,这取决于10位周期内字对齐指针的初始位置。如果10位的采样窗口能很好地捕获对齐字符(如图3a所示),那就没有延时。如果采样窗口没有与字符对齐,则将导致多达9位周期的延时(如图3b所示)。对于工作频率为2.488Gbps(400ps周期)的CPRI链路,这意味最坏延迟变化为±1.8ns。

图3:字对齐导致的延时变化。

采用基于SERDES的FPGA混合结构,还需要桥接FIFO来支持从高速PCS时钟到FPGA时钟域的转换。通过设计,这个FIFO可导致多达2个并行时钟周期的延时变化。在2.488Gbps的线速下,PCS并行时钟以该速率的十分之一运行,时钟周期大约为4ns。因此,FIFO(Tx&Rx)的每个方向上都有±8ns的最大延迟变化,这导致一共±16ns的延迟变化。

使情况变得更糟糕的是设计者没有预见到这些延时变化。因此不能在系统级估计和补偿这些变化,在支持诸如分集传输和GPS服务时,这是主要的问题。

图4:桥接FIFO导致的延时变化。

针对基于FPGA的传统嵌入式SERDES/PCS,表1总结了导致整个执行时间发生的主要因素,并与CPRI规范进行了比较。分析这些数目,可很清楚看到字对齐和桥接FIFO对大的延时变化起主要作用,导致超过规范的来回行程延时容忍度。

幸运的是,通过对传统的实现做一些小的修改就可以解决这个问题。用户可以绕过嵌入式数字PCS功能,在FPGA中实现这些逻辑。因为现在的逻辑运行在单个FPGA时钟域中,所以这个方法不再需要桥接FIFO,并且设计者可以访问导致延时的字对齐电路。在FPGA逻辑里可以通过访问寄存器的方式来获得字对齐电路测量到的延迟信息,而从在系统级针对延时变化进行补偿。这些补偿允许无线头之间在指定的窗口内进行传输以支持前面提到的业务,诸如分集传输和GPS。图5给出了低延迟设计的实现方案,关键元件都在FPGA逻辑中实现。

如果采用这个推荐的实现方案,则不再需要导致大的延时变化的单元,即省去了桥接FIFO。可访问字对齐电路的寄存器使用户能计算并进行系统级补偿,以确保不同无线头的传输都在规定的时序窗内进行。当然,模拟SERDES和CPRI IP,或者设计本身仍然存在延时,但此时整个配置的精确度已得到大大改善,可以在多跳应用中使用。该方案占用的器件资源很小,新的模块只需几百个LUT。表2列出了这个配置中新的延时变化。可以看到总的延时变化大大下降。对单跳来说这很容易满足来回行程延时规范,对支持多达4级的多跳应用是足够的低。

图5:低延迟设计的实现方案,其中关键元件都在FPGA逻辑中实现。

无线电 LTE 放大器 嵌入式 收发器 FPGA 功率放大器 电压 GPS 电路 滤波器 DSP 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)

- 选择合适的FPGA千兆位收发器至关重要(10-28)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- QPSK调制器的FPGA实现(03-22)

- 基于CPLD与单片机的高速数据采集系统(04-08)