QPSK调制器的FPGA实现

时间:03-22

来源:互联网

点击:

1 引言

四相绝对移相键控(QPSK)技术以其抗干扰性能强、误码性能好、频谱利用率高等优点,广泛应用于数字通信系统。随着超大规模集成电路的出现,FPGA在数字通信系统中的应用日益广泛,目前已提出了多种基于FPGA实现QPSK的方法。

本文基于FPGA实现直接数字频率合成(DDS),通过对DDS信号f载波信号1输出相位的控制实现调相,除DA转换外,其它过程均口『以FPGA实现。

2 QPSK调制的基本原理

QPSK采用四种不同的载波相位来表示数字信息,每个载波相位代表2比特信息,其实现有两种方法,相位选择法与正交调制法,相位选择法又分为A、B两种方式。本文采用相位选择法B方式来实现QPSK信号,如图1所示。

图1相位选择法产生QPSK信号

3 QPSK调制电路的FPGA实现

3.1串并转换电路

图2串并转换电路

调制信号(DATA)形成双比特码兀QI口】由图2所不串并转换电路实现。

假设涮制信号为01100011,其时序图如图3所示。从时序图可以看出,从第3个时钟脉冲开始,每2个时钟脉冲,在Q3、Q6同时输出DATA的连续2bit数据,生成双比特码元QI,双比特码元速率为时钟信号(CLKl)频率的一半。为了配合后面的相位调制电路,时钟信号(CLKl)频率为系统时钟频率k的I/M,可以通过M分频电路实现。

图3串并变换电路时序图

3.2四相载波产生器

四相载波产毕器甚干DDS构成.如图4所示。

图4基于DDS的四相载波产生电路

(1)建立正弦查找表

ROM正弦查找表存储了一个完整正弦波周期的抽样值,设相位累加器的数据线宽度为N,则有2一个采样点。先用其他工具计算出这2n个采样点的幅度值,则相邻2个采样点的相位增三个时钟后,相应的载波初始相位、幅艘值与理论分析是一致量为2π/2n,这样,各采样点的位置就确定了该采样点的相位;以ROM依次存储2n个采样点的幅度值,便建立了各采样相位(存储器地址)与幅值的影射关系。

然后用Quartus 5.1建立mif文件,调用LPM_ROM模块,将mif文停的数据内容写入LPM_ROM。

(2)相位累加器

设相位累加器的初始值为0,累加步长为频率控制字K.则每一个时钟周期(1/fclk)的相位增量为K×2π2n,一个完整正弦波周期需要进行2π(Kx2/2n)=2N/K次累加,所以输出信号周期10t=(I/fclk)X2N/K,输出信号频率fout=Kxfclk/2n。

(3)逻辑选相电路

双比特序列QI作为相位控制字用于四种相位载波的选择控制。本文取N:10,先计算出这210=1024个采样点的幅度值,量化为8位二进制数表示。相位为π/4和3π/4时,对应幅度值为38,存储地址分别为000111111l和0101111111。

本义中用VHD语句来完成逻辑选相电路。

if clk"event and clk=’l’then

b<=QI(1);

c<=QI(0);

if (clklh='1' or clkll='1' or clk2h=1’or clk21='1')then -- 每个双比特码元的上升沿

case QI is

when”00”=>uuu<=”100111111l”;reset<=‘1’;--5π/4载波

when”Ol”=>uuu<-”01011111Il”;reset<=‘1’;--3π/4载波

when”10”=>UUll<=”1101111111”;reset<=‘1’;--7π/4载波

when’’11”=>uuu<-”0001111111”;reset<=‘I’; --4载波

when others=>uuu<=”0000000000”;reset<=‘l’

end ease;

else uuu<=uuu+“0001000000”;reset<=‘0’;

endif;

(5)相位调制器

在每个双比特码元的上升沿产生一复位信号(RESET)使DDS的棚位累加器清零,则输出裁波信号的初始相位仅由相位控捌字控制,以保证初始相位为0l码元对应的载波相位;而其它情提下将其与相位累加器的输出相加,共同作为载波信号的相位,从而实现调相。

4 仿真实验及结论

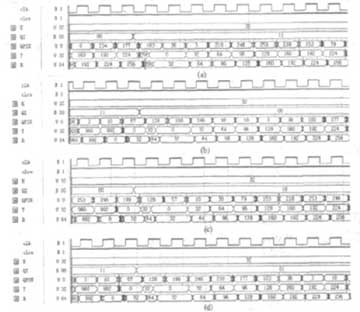

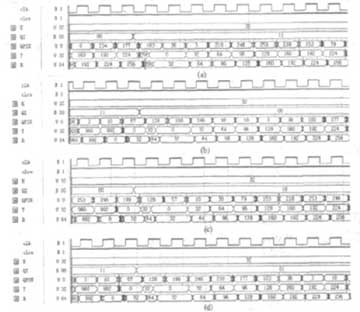

仿真实验中,取fclk=294912Hz,M=48,K=32,则fclk=fclk/M=6144Hz,载波频率fout=Kxfclk/2N=9216Hz。通过Quartusll 5.1软件仿真.得到仿真结果如图5所示。

在图(5)中,当QI为11时的第一个时钟,RESET信号对DDS寄存器复位(T=0),累加器中的加法器输出R=32,并保持一个时钟;第三个时钟后QPSK输出为218,这与QI为11时,载波初始相位为π/4、幅度值为218是一致的。间样,当QI为00、lO、Ol的仿真结果分剐如图5(b)、5(c)、5(d)所示,在QI码元到达三个时钟后,相应的载波初始相位、幅度值与理论分析时一致的。虽然QPSK信号有三个时钟的延迟,但由于各QI码元的延迟都是一致的,并不影响QPSK的实现;另一方面,延迟时间不到系统时钟周期的三分之一,可以忽略。

图5仿真实验波形

5 结束语

本文采用FPGA实现QPSK调制器克服了传统的模拟调制器的体积大、成本高、系统调试难和生产周期长等缺点。本文作者创新点在予除了DA转换外,系统全部由FPGA实现,对于其它调制方式(如DQPSK、8PSK、QAM等)的FPGA实现,以及FPGA在软件无线电钟的应用具有一定的参考价值。

作者:谢海霞 来源:微计算机信息杂志旬刊

四相绝对移相键控(QPSK)技术以其抗干扰性能强、误码性能好、频谱利用率高等优点,广泛应用于数字通信系统。随着超大规模集成电路的出现,FPGA在数字通信系统中的应用日益广泛,目前已提出了多种基于FPGA实现QPSK的方法。

本文基于FPGA实现直接数字频率合成(DDS),通过对DDS信号f载波信号1输出相位的控制实现调相,除DA转换外,其它过程均口『以FPGA实现。

2 QPSK调制的基本原理

QPSK采用四种不同的载波相位来表示数字信息,每个载波相位代表2比特信息,其实现有两种方法,相位选择法与正交调制法,相位选择法又分为A、B两种方式。本文采用相位选择法B方式来实现QPSK信号,如图1所示。

图1相位选择法产生QPSK信号

3 QPSK调制电路的FPGA实现

3.1串并转换电路

图2串并转换电路

调制信号(DATA)形成双比特码兀QI口】由图2所不串并转换电路实现。

假设涮制信号为01100011,其时序图如图3所示。从时序图可以看出,从第3个时钟脉冲开始,每2个时钟脉冲,在Q3、Q6同时输出DATA的连续2bit数据,生成双比特码元QI,双比特码元速率为时钟信号(CLKl)频率的一半。为了配合后面的相位调制电路,时钟信号(CLKl)频率为系统时钟频率k的I/M,可以通过M分频电路实现。

图3串并变换电路时序图

3.2四相载波产生器

四相载波产毕器甚干DDS构成.如图4所示。

图4基于DDS的四相载波产生电路

(1)建立正弦查找表

ROM正弦查找表存储了一个完整正弦波周期的抽样值,设相位累加器的数据线宽度为N,则有2一个采样点。先用其他工具计算出这2n个采样点的幅度值,则相邻2个采样点的相位增三个时钟后,相应的载波初始相位、幅艘值与理论分析是一致量为2π/2n,这样,各采样点的位置就确定了该采样点的相位;以ROM依次存储2n个采样点的幅度值,便建立了各采样相位(存储器地址)与幅值的影射关系。

然后用Quartus 5.1建立mif文件,调用LPM_ROM模块,将mif文停的数据内容写入LPM_ROM。

(2)相位累加器

设相位累加器的初始值为0,累加步长为频率控制字K.则每一个时钟周期(1/fclk)的相位增量为K×2π2n,一个完整正弦波周期需要进行2π(Kx2/2n)=2N/K次累加,所以输出信号周期10t=(I/fclk)X2N/K,输出信号频率fout=Kxfclk/2n。

(3)逻辑选相电路

双比特序列QI作为相位控制字用于四种相位载波的选择控制。本文取N:10,先计算出这210=1024个采样点的幅度值,量化为8位二进制数表示。相位为π/4和3π/4时,对应幅度值为38,存储地址分别为000111111l和0101111111。

本义中用VHD语句来完成逻辑选相电路。

if clk"event and clk=’l’then

b<=QI(1);

c<=QI(0);

if (clklh='1' or clkll='1' or clk2h=1’or clk21='1')then -- 每个双比特码元的上升沿

case QI is

when”00”=>uuu<=”100111111l”;reset<=‘1’;--5π/4载波

when”Ol”=>uuu<-”01011111Il”;reset<=‘1’;--3π/4载波

when”10”=>UUll<=”1101111111”;reset<=‘1’;--7π/4载波

when’’11”=>uuu<-”0001111111”;reset<=‘I’; --4载波

when others=>uuu<=”0000000000”;reset<=‘l’

end ease;

else uuu<=uuu+“0001000000”;reset<=‘0’;

endif;

(5)相位调制器

在每个双比特码元的上升沿产生一复位信号(RESET)使DDS的棚位累加器清零,则输出裁波信号的初始相位仅由相位控捌字控制,以保证初始相位为0l码元对应的载波相位;而其它情提下将其与相位累加器的输出相加,共同作为载波信号的相位,从而实现调相。

4 仿真实验及结论

仿真实验中,取fclk=294912Hz,M=48,K=32,则fclk=fclk/M=6144Hz,载波频率fout=Kxfclk/2N=9216Hz。通过Quartusll 5.1软件仿真.得到仿真结果如图5所示。

在图(5)中,当QI为11时的第一个时钟,RESET信号对DDS寄存器复位(T=0),累加器中的加法器输出R=32,并保持一个时钟;第三个时钟后QPSK输出为218,这与QI为11时,载波初始相位为π/4、幅度值为218是一致的。间样,当QI为00、lO、Ol的仿真结果分剐如图5(b)、5(c)、5(d)所示,在QI码元到达三个时钟后,相应的载波初始相位、幅度值与理论分析时一致的。虽然QPSK信号有三个时钟的延迟,但由于各QI码元的延迟都是一致的,并不影响QPSK的实现;另一方面,延迟时间不到系统时钟周期的三分之一,可以忽略。

图5仿真实验波形

5 结束语

本文采用FPGA实现QPSK调制器克服了传统的模拟调制器的体积大、成本高、系统调试难和生产周期长等缺点。本文作者创新点在予除了DA转换外,系统全部由FPGA实现,对于其它调制方式(如DQPSK、8PSK、QAM等)的FPGA实现,以及FPGA在软件无线电钟的应用具有一定的参考价值。

作者:谢海霞 来源:微计算机信息杂志旬刊

集成电路 FPGA 电路 Quartus 仿真 无线电 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)