ASIC中的异步FIFO的实现

时间:10-05

来源:互联网

点击:

5 异步FIFO的VHDL实现

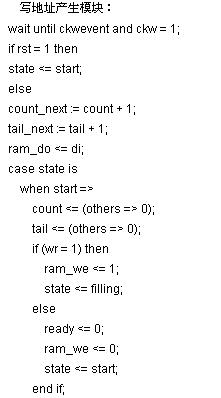

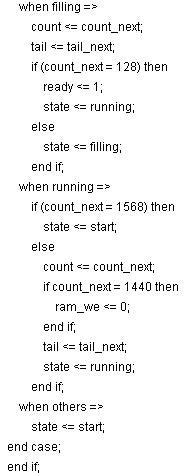

VHDL是硬件描述语言的一种,用于数字电子系统设计。设计者可用它进行各种级别的逻辑设计,可用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件描述语言。目前VHDL语言已经得到多种EDA工具的支持,并且已经成为IEEE标准,因此利用VHDL语言进行电路设计可以节约开发成本和周期。下面以视频转换系统中的异步FIFO为例,用VHDL实现如下(假设存储器的深度为128个像素,即256个字节):

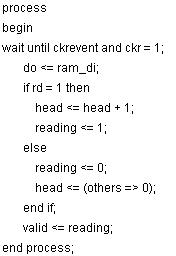

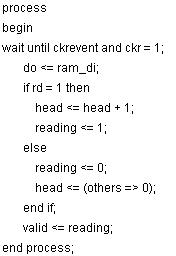

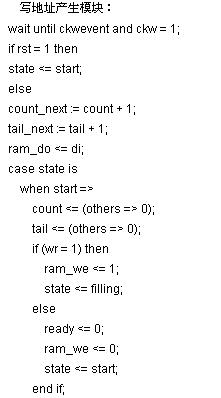

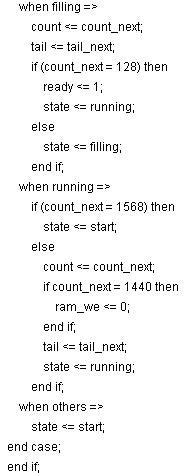

读地址产生模块:

6 结论

本文作者创新点:本文讨论了在ASIC设计中数据在不同时钟之间传递数据所产生的亚稳态问题,并提出了一种新的异步FIFO的设计方法,并用VHDL语言进行描述,利用Altera公司的Cyclone系列的EP1C6进行硬件实现,该电路软件仿真和硬件实现已经通过验证,并应用到各种电路中。实践证明它可以解决由于异步产生的错误,同时增加了应用的灵活性。

VHDL是硬件描述语言的一种,用于数字电子系统设计。设计者可用它进行各种级别的逻辑设计,可用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件描述语言。目前VHDL语言已经得到多种EDA工具的支持,并且已经成为IEEE标准,因此利用VHDL语言进行电路设计可以节约开发成本和周期。下面以视频转换系统中的异步FIFO为例,用VHDL实现如下(假设存储器的深度为128个像素,即256个字节):

读地址产生模块:

6 结论

本文作者创新点:本文讨论了在ASIC设计中数据在不同时钟之间传递数据所产生的亚稳态问题,并提出了一种新的异步FIFO的设计方法,并用VHDL语言进行描述,利用Altera公司的Cyclone系列的EP1C6进行硬件实现,该电路软件仿真和硬件实现已经通过验证,并应用到各种电路中。实践证明它可以解决由于异步产生的错误,同时增加了应用的灵活性。

电路 集成电路 VHDL 电子 仿真 EDA Altera 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)