利用CPLD降低处理器功耗

时间:09-25

来源:互联网

点击:

- 系统中断

根据处理器的最终应用,有多种外部器件可以中断处理器。这些中断信号包括数据采集和数据处理两种请求。现在,通过分离对微处理器的数据处理请求,可以由外部 CPLD 来处理数据采集请求。利用 CPLD 来处理数据采集中断可以卸载对微处理器的中断请求,从而降低功耗。

是否可将数据采集中断类型划归 CPLD 取决于最终应用。可以将要求对输入数据予以响应的外设或输入数据划为数据采集中断请求类型。数据采集中断包括:

- 存储器存取中断

- I2C、UART、SPI 和 ISA 等通信接口

- 通用 I/O 中断

- LCD 接口中断

这并非可由 CPLD 处理的中断的完整列表,只是为系统设计提供一个起点。

操作流程

图 5 所示为 CPLD 设计的主要操作流程。CPLD 一旦识别出有效的外部中断,就会自我判断是否具有处理该中断的功能。CPLD 处理该中断之后,会向处理器发出一个中断申请,请求其进行所要求的数据处理。CPLD 如果不能处理该中断,则将其传递给处理器。CPLD 还负责监测处理器的操作状态。

功能

低功耗 CPLD 设计由处理中断请求的中断接口和控制器、处理中断的功能以及处理器接口组成。下面分别详述 CPLD 的各主要功能:

- 系统器件的中断接口

- 中断控制器

- 用于中断处理的外设接口

- 微处理器中断接口

- 微处理器操作模式接口

- 中断接口

CPLD 的中断接口接收经过微处理器识别的所有外部器件的中断请求。该中断接口判断 CPLD 是否有能力处理相应的中断请求。CPLD 对请求数据接收和存储功能的数据采集中断进行处理。CPLD 如果不能处理该中断,则将其传递给微处理器。

CPLD 的中断接口为所有中断源提供屏蔽功能,并且具有判断中断源的能力。可编程逻辑能够灵活地改变触发模式,包括高低电平敏感触发模式和升降沿敏感触发模式。CPLD 的中断控制寄存器与微处理器中的寄存器相似。

中断控制器

CPLD 的中断控制器模拟系统微处理器中的功能。该中断控制器判断数据采集中断来自哪个器件,然后启动中断处理。CPLD 处理本该由微处理器处理的数据采集中断请求。

中断控制器启动处理请求的操作。由 CPLD 从远程器件接收数据的应用就是这样的例子。该器件请求将所传送的数据写入存储器。CPLD 的中断控制器识别出有效中断,然后启动存储器接口来解译数据。

外设接口

CPLD 提供处理中断请求所需的系统器件接口。所需器件接口取决于最终应用。如果外部器件向 CPLD 发出中断请求,要求对存储元件进行数据读写操作,则 CPLD 设计中就需具备该存储器的接口。所需接口类型可以为存储器接口、LCD 接口以及 PCI、UART、SPI 和 ISA 等通信接口。

微处理器中断接口

像请求处理器提供服务的所有外部器件一样,CPLD 也具有向微处理器发出中断的功能。CPLD 必须能够在完成数据采集操作之后向微处理器发出中断。设计人员可以为来自 CPLD 的中断请求设置优先级,并可选择该中断是否唤醒处于断电状态的处理器。

微处理器操作模式接口

CPLD 是否能识别处理器的操作状态取决于系统微处理器。有些微处理器提供表示当前操作模式的外部引脚。CPLD 可能会识别出处理器的当前操作状态,并且确定是否向处理器发出执行等待中断的请求,这取决于 CPLD 和微处理器的设计。例如,如果 CPLD 接收到低优先级中断,而处理器无需从低功耗状态转至其他状态,则 CPLD 可以创建一个寄存器以指示将中断挂起。然后,当处理器苏醒时,可由微处理器读取挂起中断的寄存器。

优点

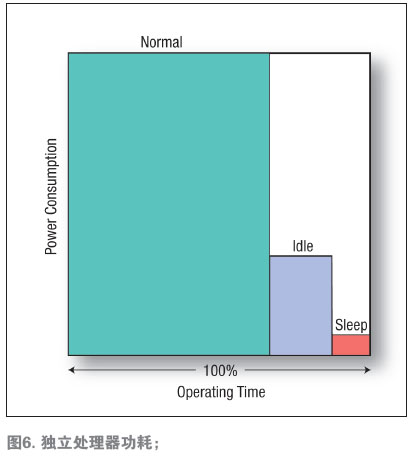

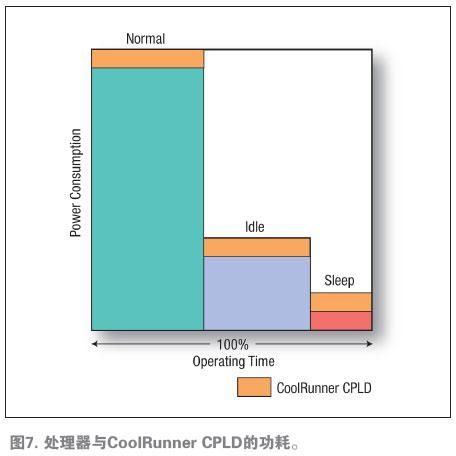

图 6 和图 7 所示为可在一种典型电池供电器件中实现的节电效果;其中图 7 所示为使用先进的低功耗 CPLD,图 6 所示为使用独立的微处理器设计。与通过延长微处理器低功耗模式所实现的节电效果相比,CPLD 的功耗要求微不足道。典型低功耗 CPLD 的待机电流约为 100μA。操作功耗取决于应用和时钟频率。对于充满 16 位计数器和 50MHz 时钟的 64 宏单元的 CPLD 来说,ICC 约为 10mA。请注意,所实现的实际节电效果取决于系统设计,包括微处理器类型和 CPLD 设计。

随着用 CPLD 获得节电效果,中断响应时间也缩短了。外设不必再等待微处理器从节电状态苏醒的延迟时间。可以实现的其他设计节省项包括:

- 减少对处理器的中断请求数

- 减少一定时长上的处理器唤醒周期数

- 在不影响吞吐量的情况下降低时钟频率

- 进行数据处理操作时以较低频率运行处理器

- 进行数据采集操作时以较高频率运行 CPLD

结论

设计功耗敏感型应用不仅涉及使用软件进行电源管理,还涉及运用硬件设计技巧。通过设计低功耗 CPLD 来延长微处理器的低功耗操作状态,可以显著降低系统功耗。当今市场上的最新 CPLD 可以为任何最终应用提供低功耗和高速度的灵活组合应用。

- 系统中断

CPLD 电子 电压 电流 总线 电容 PCB ARM 电源管理 LCD 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)