Top Down FPGA设计的黄金组合

时间:09-15

来源:互联网

点击:

电子技术的日新月异,不断地改变着人们的生活方式。而世界电子技术及设计方法的发展,正在给中国的电子设计工程师们以新的挑战和压力。不能否认,目前中国电子设计技术仍远远落后于发达国家水平,尤其是在电子技术的基础产业,即IC/ASIC方面。当国人以国产计算机,电视,VCD,影碟机等产业欣欣向荣,飞速发展而沾沾自喜的时候,却不能不看到,几乎所有的核心技术和几乎所有的内部关键集成电路,仍然印着国外半导体厂家的商标。单从时间上看,国内技术可能只落后一、二十年,但是我们更应该看到:一方面,这一产业的发展是以非线性速度向前推进的,另一方面,当发达国家“全民皆兵”,整体发展水平平均较高时,国内仍局限在为数不多的几个国家重点投资企业或合资/独资企业里。

然而,我们有幸的看到,FPGA/EPLD的发展正逐步取代越来越多的ASIC市场。可重复使用,小批量,低投入,高性能,高密度,开发周期短等诸多优点,使国内更多的工程师们乐于采用。由于不需要任何投片费用,也不需要建立任何生产线,因此,采用FPGA/EPLD所需的投资远远低于ASIC的投资。据估计,引进一套先进的FPGA Top-Down设计工具所需费用还不到ASIC所需的十分之一,而大力推广先进的FPGA设计方法,既可以降低诸多产业投资成本,也可培养一大批国内的Top-Down的设计人才,从而提高国内Top-Down设计的整体水平,为将来国内ASIC产业的快速、健康发展打下坚实的基础。

FPGA/EPLD的自上而下(Top-Down)设计方法:

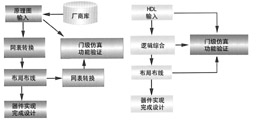

传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特定FPGA/EPLD厂商布局布线器所需网表,通过布局布线,完成设计。原理图绘制完成后可采用门级仿真器进行功能验证。

图1:传统的设计手段与Top-Down设计工具的比较

然而,工程师的最初设计思想不是一开始就考虑采用某一FPGA/EPLD厂商的某一特定型号器件,而是从功能描述开始的。设计工程师首先要考虑规划出能完成某一具体功能、满足自己产品系统设计要求的某一功能模块,利用某种方式(如HDL硬件描述语言)把功能描述出来,通过功能仿真(HDL仿真器)以验证设计思路的正确性。当所设计功能满足需要时,再考虑以何种方式(即逻辑综合过程)完成所需要的设计,并能直接使用功能定义的描述。实际上这就是自顶而下设计方法。

与传统电原理图输入设计方法相比,Top-Down设计方法具体有以下优点:

1、完全符合设计人员的设计思路,从功能描述开始,到物理实现的完成。

2、功能设计可完全独立于物理实现

在采用传统的电原理输入方法时,FPGA/EPLD器件的采用受到器件库的制约。由于不同厂商FPGA/EPLD的结构完全不同,甚至同一厂商不同系列的产品也存在结构上的差别,因此,在设计一开始,工程师的设计思路就受到最终所采用器件的约束,大大限制了设计师的思路和器件选择的灵活性。而采用Top-Down设计方法,功能输入采用国际标准的HDL输入方法,HDL可不含有任何器件的物理信息,因此工程师可以有更多的空间去集中精力进行功能描述,设计师可以在设计过程的最后阶段任意选择或更改物理器件。

3、设计可再利用

设计结果完全可以以一种知识产权(IP-Intellectual Property)的方式作为设计师或设计单位的设计成果,应用于不同的产品设计中,做到成果的再利用。

4、易于设计的更改

设计工程师可在极短的时间内修改设计,对各种FPGA/EPLD结构进行设计结果规模(门消耗)和速度(时序)的比较,选择最优方案。

5、设计、处理大规模、复杂电路

目前的FPGA/EPLD器件正向高集成度、深亚微米工艺发展。为设计系统的小型化,低功耗、高可靠性等提供了集成的手段。设计低于一万门左右的电路,Top-Down设计方法具有很大的帮助,而设计更大规模的电路,Top-Down设计方法则是必不可少的手段。

6、设计周期缩短,生产率大大提高,产品上市时间提前,性能明显提高,产品竞争力加强。据统计,采用Top-Down设计方法的生产率可达到传统设计方法的2到4倍。

Top-Down设计流程如图2所示,其核心是采用HDL语言进行功能描述,由逻辑综合(Logic Synthesis)把行为(功能)描述转换成某一特定FPGA/EPLD的工艺网表,送到厂商的布局布线器完成物理实现。在设计过程的每一个环节,仿真器的功能验证和门级仿真技术保证设计功能和时序的正确性。

然而,我们有幸的看到,FPGA/EPLD的发展正逐步取代越来越多的ASIC市场。可重复使用,小批量,低投入,高性能,高密度,开发周期短等诸多优点,使国内更多的工程师们乐于采用。由于不需要任何投片费用,也不需要建立任何生产线,因此,采用FPGA/EPLD所需的投资远远低于ASIC的投资。据估计,引进一套先进的FPGA Top-Down设计工具所需费用还不到ASIC所需的十分之一,而大力推广先进的FPGA设计方法,既可以降低诸多产业投资成本,也可培养一大批国内的Top-Down的设计人才,从而提高国内Top-Down设计的整体水平,为将来国内ASIC产业的快速、健康发展打下坚实的基础。

FPGA/EPLD的自上而下(Top-Down)设计方法:

传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特定FPGA/EPLD厂商布局布线器所需网表,通过布局布线,完成设计。原理图绘制完成后可采用门级仿真器进行功能验证。

图1:传统的设计手段与Top-Down设计工具的比较

然而,工程师的最初设计思想不是一开始就考虑采用某一FPGA/EPLD厂商的某一特定型号器件,而是从功能描述开始的。设计工程师首先要考虑规划出能完成某一具体功能、满足自己产品系统设计要求的某一功能模块,利用某种方式(如HDL硬件描述语言)把功能描述出来,通过功能仿真(HDL仿真器)以验证设计思路的正确性。当所设计功能满足需要时,再考虑以何种方式(即逻辑综合过程)完成所需要的设计,并能直接使用功能定义的描述。实际上这就是自顶而下设计方法。

与传统电原理图输入设计方法相比,Top-Down设计方法具体有以下优点:

1、完全符合设计人员的设计思路,从功能描述开始,到物理实现的完成。

2、功能设计可完全独立于物理实现

在采用传统的电原理输入方法时,FPGA/EPLD器件的采用受到器件库的制约。由于不同厂商FPGA/EPLD的结构完全不同,甚至同一厂商不同系列的产品也存在结构上的差别,因此,在设计一开始,工程师的设计思路就受到最终所采用器件的约束,大大限制了设计师的思路和器件选择的灵活性。而采用Top-Down设计方法,功能输入采用国际标准的HDL输入方法,HDL可不含有任何器件的物理信息,因此工程师可以有更多的空间去集中精力进行功能描述,设计师可以在设计过程的最后阶段任意选择或更改物理器件。

3、设计可再利用

设计结果完全可以以一种知识产权(IP-Intellectual Property)的方式作为设计师或设计单位的设计成果,应用于不同的产品设计中,做到成果的再利用。

4、易于设计的更改

设计工程师可在极短的时间内修改设计,对各种FPGA/EPLD结构进行设计结果规模(门消耗)和速度(时序)的比较,选择最优方案。

5、设计、处理大规模、复杂电路

目前的FPGA/EPLD器件正向高集成度、深亚微米工艺发展。为设计系统的小型化,低功耗、高可靠性等提供了集成的手段。设计低于一万门左右的电路,Top-Down设计方法具有很大的帮助,而设计更大规模的电路,Top-Down设计方法则是必不可少的手段。

6、设计周期缩短,生产率大大提高,产品上市时间提前,性能明显提高,产品竞争力加强。据统计,采用Top-Down设计方法的生产率可达到传统设计方法的2到4倍。

Top-Down设计流程如图2所示,其核心是采用HDL语言进行功能描述,由逻辑综合(Logic Synthesis)把行为(功能)描述转换成某一特定FPGA/EPLD的工艺网表,送到厂商的布局布线器完成物理实现。在设计过程的每一个环节,仿真器的功能验证和门级仿真技术保证设计功能和时序的正确性。

电子 集成电路 半导体 FPGA 电路 仿真 Mentor ModelSim VHDL Verilog Altera Atmel Cypress Xilinx 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)