基于CPLD的容错存储器的设计实现

时间:09-14

来源:互联网

点击:

2.3电路输入输出设计

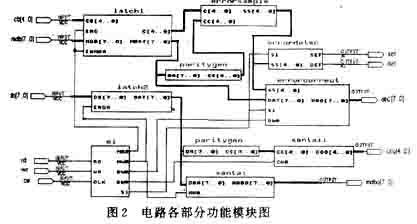

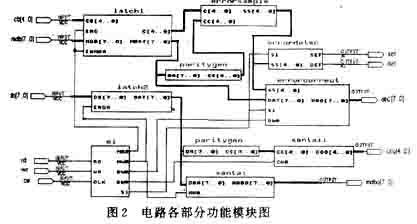

RD,WR,CLK为CPU输入到纠检错信号,通过控制电路产生芯片内控制信号。在写信号时,DB[7..0]从数据总线输入,通过锁存以后经过三态控制(Santai模块)写入到存储器,同时数据通过校验码产生模块(Paritygen)产生5 b校验码,通过三态控制写入冗余存储器。读信号时,存储器数据读入纠检错电路经过锁存后产生5 b校验码,同时与从冗余存储器读入的5 b检验码一起通过错误图样模块(Errorsample),产生错误图样。通过错误图样检测错误,当数据产生错误时通过纠错模块(Errorcorrect)纠错后将正确数据输出到数据总线。Errordetec为错误状态模块,SEF,DEF为错误状态信号。0,0时无错,1,0时1位错,1,1时2位错。电路实现的各部分功能模块如图2所示。

3 仿真及其波形

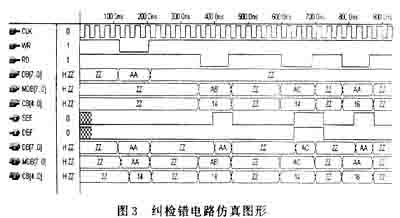

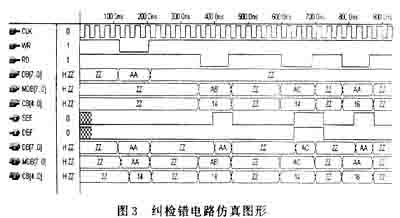

本文采用Altera公司的CPLD器件EPM7128作为设计环境 ,图3是纠检错电路仿真图形,用CPLD实现纠检错电路仿真,图中118~205 ns时从数据线上写入数据AA,359~443 ns时仿真了读数据时产生1位错情况,601~692 ns时仿真了产生2位错情况,此时检测到了2位错,但是不能纠正。781~863 ns时仿真了校验位产生1位错时的情况。

4 分析与结论

本文利用最佳奇权码的基本原理设计的纠错码电路可以校正单位错,检出2位错,存储器不因单位错而中断工作,故其平均无故障时间MTBF增大,提高了可靠性。但是纠一检二码的新增器材又使MTBF有所下降。

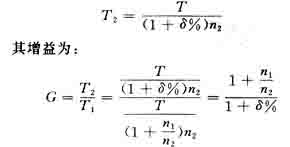

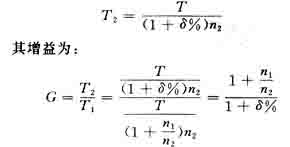

在效率上,设在时间T内,发生1位错的次数为n 1 ,发生2位及多位错的次数为n 2 ,采用纠错码时,平均无故障时间为T 1 =T/(n 1 +n 2 ),采用最佳奇权码后,1位错是可纠的,仅2位及多位错是不可纠的,作为出错处理。设由于采用纠错码而增加器材δ%,因而采用最佳奇权码后的平均无故障时间为:

据资料估计,对于1位错占整个错误的比例 ,增益G=4.6~9.3。通过CPLD来实现存储器的容错,大大缩短了设计开发周期,降低了成本,同时提高了系统的可靠性。

,增益G=4.6~9.3。通过CPLD来实现存储器的容错,大大缩短了设计开发周期,降低了成本,同时提高了系统的可靠性。

RD,WR,CLK为CPU输入到纠检错信号,通过控制电路产生芯片内控制信号。在写信号时,DB[7..0]从数据总线输入,通过锁存以后经过三态控制(Santai模块)写入到存储器,同时数据通过校验码产生模块(Paritygen)产生5 b校验码,通过三态控制写入冗余存储器。读信号时,存储器数据读入纠检错电路经过锁存后产生5 b校验码,同时与从冗余存储器读入的5 b检验码一起通过错误图样模块(Errorsample),产生错误图样。通过错误图样检测错误,当数据产生错误时通过纠错模块(Errorcorrect)纠错后将正确数据输出到数据总线。Errordetec为错误状态模块,SEF,DEF为错误状态信号。0,0时无错,1,0时1位错,1,1时2位错。电路实现的各部分功能模块如图2所示。

3 仿真及其波形

本文采用Altera公司的CPLD器件EPM7128作为设计环境 ,图3是纠检错电路仿真图形,用CPLD实现纠检错电路仿真,图中118~205 ns时从数据线上写入数据AA,359~443 ns时仿真了读数据时产生1位错情况,601~692 ns时仿真了产生2位错情况,此时检测到了2位错,但是不能纠正。781~863 ns时仿真了校验位产生1位错时的情况。

4 分析与结论

本文利用最佳奇权码的基本原理设计的纠错码电路可以校正单位错,检出2位错,存储器不因单位错而中断工作,故其平均无故障时间MTBF增大,提高了可靠性。但是纠一检二码的新增器材又使MTBF有所下降。

在效率上,设在时间T内,发生1位错的次数为n 1 ,发生2位及多位错的次数为n 2 ,采用纠错码时,平均无故障时间为T 1 =T/(n 1 +n 2 ),采用最佳奇权码后,1位错是可纠的,仅2位及多位错是不可纠的,作为出错处理。设由于采用纠错码而增加器材δ%,因而采用最佳奇权码后的平均无故障时间为:

据资料估计,对于1位错占整个错误的比例

,增益G=4.6~9.3。通过CPLD来实现存储器的容错,大大缩短了设计开发周期,降低了成本,同时提高了系统的可靠性。

,增益G=4.6~9.3。通过CPLD来实现存储器的容错,大大缩短了设计开发周期,降低了成本,同时提高了系统的可靠性。

电路 集成电路 半导体 电容 CPLD 总线 仿真 Altera 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)