以太网到多路E1适配电路设计及FPGA实现

时间:09-14

来源:互联网

点击:

2.2 E1接收数据同步

E1接收侧要完成的功能是从多路E1数据中还原出以太网数据包。简单看就是发送侧反向复用的逆过程,通过高速时钟循环从1→n路E1中各读出一字节合成一路数据。但由于各路E1在传递过程中经过延时不同,同一时刻到达字节不对齐,在合并前必须对多路E1进行同步。考虑到同步过程的复杂性,在设计算法时采用了分步处理,以降低复杂度。

第一步处理是根据帧结构中帧同步码,通过置位同步法完成单路E1帧同步,同步原理图和状态机如图3所示。同步后每路输出数据产生独立的帧定时计数器TM,从0→31标记E1帧对应的32(256bit)字节,其中第0字节即帧同步码Framecode,第一字节即复帧计数器MFcnt。这一步并未涉及多路间的延时消除。

根据状态转移图确定的状态参数,α(搜索保护帧数)=3、β(同步保护帧数)=4。设线中误码率Pe=10-3,L(帧同步码长度)=8,Ts(E1帧周期)=125μs,得出同步机的性能指标:

平均同步时间≈[1/(L×Pe)β-(α-1/2)] ×Ts≈8.5小时

同步失帧误码率≈1/2(α-1/2)(L×Pe)β≈5×10 -9

可见在较高的误码率下(10 -3),同步机还是能够保证比较好的同步质量,平绝每8.5小时出现一次失步,引入的附加误码率也只有10 -9量级。

第二步处理根据E1帧同步产生的帧计数和每感数据中的复帧计数消除各之间的延时及时钟相位差。其基本原理见图4。在第0路数据延时最小的情况下,设第一步完成同步后到达RAM(0)的数据为第M复帧第T字节,数据以各自计数为写地址存入RAM,延时检测通过计数不停检测,直到所有路第M复帧T字节到达后,再统一以clk为读时钟,以M&T为起始地址顺序从RAM中读出数据。由于MFcnt最大为255,第二步同步能容纳的线路时延在(-128,+128)帧之间,超过这个范围MFcnt所代表的时延就可能是(n(任意整数) ×128+MFcnt)帧,所以该算法能承受的最大线路延时为:

128×Ts(帧周期)=16ms

在线路误码率较低时,E1帧同步丢失较少,帧定时计数TM可以确定,影响第二步处理的只有数据中的复帧计数字节。在没有保护的条件下,假设目前某一路MFcnt由于误码使其读数由正确值A变为B,因为下一轮开始时A、B位置帧会重写,不会对数据整体逻辑产生较大影响,其它位置的误码会在后续的HDLC帧同步处理中检测。如果线睡误码率较高,由于E1会频繁失步使第二步处理根本无法进行。出于述考虑该步算法设计没有采用状态机保护。

2.3 HDB3时钟提取

从接收的E1信号HDB3编码中提取时钟的原理如图5所示。首先通过一个高速时钟采样HDB3的码流(CODE)得到数据变化沿(EDGE),再根据EDGE位置由高速时钟分频出对应的2MHz时钟。

3 电路设计

整体电路结构如图6所示。在输入数据缓存和消延时两部分处理中,由于需要较大存储空间,采用两块外挂的SSRAM。内部处理以字节为单位,全同步电路设计,对应以太网侧处理速率为12.5MHz,对尖E1侧时钟为256kHz(2.048MHz/8)。两侧速率匹配通过高速时钟采样低速时钟完成。

4 时序分析

从逻辑验证到FPGA实现主要区别是增加了实现布线、引脚间的时延。使系统失效的时序问题主要有以下几点:

(1)输入经内部逻辑到输出的建立时间、保持时间和引脚时延大于一个时钟周期。

(2)并行处理的信号彼此之间时延过大,不能同时采样。

(3)在内部对时钟信号进行过多操作,引入时钟毛刺。

(4)对同一时钟,既使用上升沿,又使用下降沿触发,使时钟最高频率损失一半。

(5)在交叉时钟域中,直接采样由另一时钟作为触发的信号,引入不确定态。

对于这些常见问题,设计中采用如下相应对策:

(1)所有输入、输出引脚信号都经过时钟采样,减少引脚的时延。

(2)内部信号操作增加D触发器,两级触发器之间尽量减少组合逻辑,比较复杂的处理经多个时钟周期完成,减小信号保持时间。

(3)并行逻辑经过相同的处理流程,时分复用完成,并行引脚也尽量分配在一起。

(4)内部处理由单一系统时钟完成,低速时钟经高速时钟采样统一到高速时钟上,减少交叉时钟域。

(5)不对系统时钟进行操作,只使用上升沿触发器。

(6)必需进行时钟转换时,通过双端口RAM或FIFO完成,不直接操作交叉时钟。

在设计中注意上述问题后,QUARTUS II的后仿真结果能够很好地满足时序要求,其中系统时钟(12.5MHz)最在能够满足20.59MHz,2MHz时钟能够满足41.03MHz。此结果在实际硬件测试中得到了验证。

5 实际产品性能分析

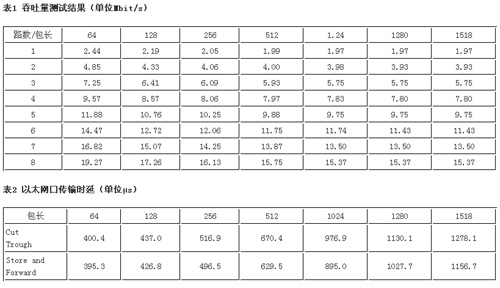

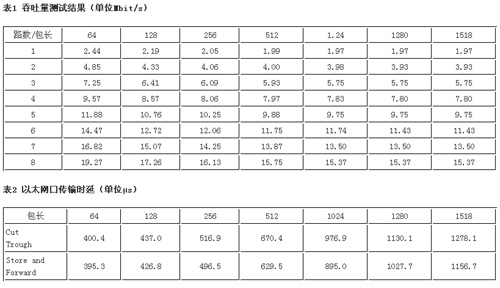

本文介绍的以太网/多路E1适配电路设计已实际应用在华环公司H0EL-1100 E1/100 Base-TX适配器中,表1是实际产品的吞吐量测试结果。由于以太网吞吐量包括IEEE802.3规定的导和SFD字节,而这部分信息是固定值,不需要经过E1信道传输到对端,所以测试值可能大于实际E1信道容量。表2是在8路E1配置下,以15MHz速率发包测得的以太网数据两端设备的传输延时。该设计在APEX II 20K100器件中占用的逻辑单元为3608个(共4160个逻辑门)。

在开发过程中由于采用高级硬件编程语言→编程器件的设计实现过程,大大缩短了开发周期,增加了硬件设计的灵活性和可移植性,也避免了专用集成电路设计的高风险。采用逻辑仿真与后时序仿真相结合的验证方法,基本可以保证设计的可靠性。基于上述优点,这种开发方式在中小指集成电路开发中已得到广泛的应用。尤其是近年来,硬件方面伴随着微电子工艺的迅速发展,编程器件的集成度正在成倍增长,越来越多的ASIC单元如微处理器、专用接口等嵌入编程器件中,使其适用范围更广;软件方面EDA开发商提供了众多的Ipcore及仿真工具,使得编程过程进一步简化,可靠性也不断增强;在此基础上SYS On Programmable Chip技术也开始走向商业化,为编程器件的发展提供了更为广阔的空间。

E1接收侧要完成的功能是从多路E1数据中还原出以太网数据包。简单看就是发送侧反向复用的逆过程,通过高速时钟循环从1→n路E1中各读出一字节合成一路数据。但由于各路E1在传递过程中经过延时不同,同一时刻到达字节不对齐,在合并前必须对多路E1进行同步。考虑到同步过程的复杂性,在设计算法时采用了分步处理,以降低复杂度。

第一步处理是根据帧结构中帧同步码,通过置位同步法完成单路E1帧同步,同步原理图和状态机如图3所示。同步后每路输出数据产生独立的帧定时计数器TM,从0→31标记E1帧对应的32(256bit)字节,其中第0字节即帧同步码Framecode,第一字节即复帧计数器MFcnt。这一步并未涉及多路间的延时消除。

根据状态转移图确定的状态参数,α(搜索保护帧数)=3、β(同步保护帧数)=4。设线中误码率Pe=10-3,L(帧同步码长度)=8,Ts(E1帧周期)=125μs,得出同步机的性能指标:

平均同步时间≈[1/(L×Pe)β-(α-1/2)] ×Ts≈8.5小时

同步失帧误码率≈1/2(α-1/2)(L×Pe)β≈5×10 -9

可见在较高的误码率下(10 -3),同步机还是能够保证比较好的同步质量,平绝每8.5小时出现一次失步,引入的附加误码率也只有10 -9量级。

第二步处理根据E1帧同步产生的帧计数和每感数据中的复帧计数消除各之间的延时及时钟相位差。其基本原理见图4。在第0路数据延时最小的情况下,设第一步完成同步后到达RAM(0)的数据为第M复帧第T字节,数据以各自计数为写地址存入RAM,延时检测通过计数不停检测,直到所有路第M复帧T字节到达后,再统一以clk为读时钟,以M&T为起始地址顺序从RAM中读出数据。由于MFcnt最大为255,第二步同步能容纳的线路时延在(-128,+128)帧之间,超过这个范围MFcnt所代表的时延就可能是(n(任意整数) ×128+MFcnt)帧,所以该算法能承受的最大线路延时为:

128×Ts(帧周期)=16ms

在线路误码率较低时,E1帧同步丢失较少,帧定时计数TM可以确定,影响第二步处理的只有数据中的复帧计数字节。在没有保护的条件下,假设目前某一路MFcnt由于误码使其读数由正确值A变为B,因为下一轮开始时A、B位置帧会重写,不会对数据整体逻辑产生较大影响,其它位置的误码会在后续的HDLC帧同步处理中检测。如果线睡误码率较高,由于E1会频繁失步使第二步处理根本无法进行。出于述考虑该步算法设计没有采用状态机保护。

2.3 HDB3时钟提取

从接收的E1信号HDB3编码中提取时钟的原理如图5所示。首先通过一个高速时钟采样HDB3的码流(CODE)得到数据变化沿(EDGE),再根据EDGE位置由高速时钟分频出对应的2MHz时钟。

3 电路设计

整体电路结构如图6所示。在输入数据缓存和消延时两部分处理中,由于需要较大存储空间,采用两块外挂的SSRAM。内部处理以字节为单位,全同步电路设计,对应以太网侧处理速率为12.5MHz,对尖E1侧时钟为256kHz(2.048MHz/8)。两侧速率匹配通过高速时钟采样低速时钟完成。

4 时序分析

从逻辑验证到FPGA实现主要区别是增加了实现布线、引脚间的时延。使系统失效的时序问题主要有以下几点:

(1)输入经内部逻辑到输出的建立时间、保持时间和引脚时延大于一个时钟周期。

(2)并行处理的信号彼此之间时延过大,不能同时采样。

(3)在内部对时钟信号进行过多操作,引入时钟毛刺。

(4)对同一时钟,既使用上升沿,又使用下降沿触发,使时钟最高频率损失一半。

(5)在交叉时钟域中,直接采样由另一时钟作为触发的信号,引入不确定态。

对于这些常见问题,设计中采用如下相应对策:

(1)所有输入、输出引脚信号都经过时钟采样,减少引脚的时延。

(2)内部信号操作增加D触发器,两级触发器之间尽量减少组合逻辑,比较复杂的处理经多个时钟周期完成,减小信号保持时间。

(3)并行逻辑经过相同的处理流程,时分复用完成,并行引脚也尽量分配在一起。

(4)内部处理由单一系统时钟完成,低速时钟经高速时钟采样统一到高速时钟上,减少交叉时钟域。

(5)不对系统时钟进行操作,只使用上升沿触发器。

(6)必需进行时钟转换时,通过双端口RAM或FIFO完成,不直接操作交叉时钟。

在设计中注意上述问题后,QUARTUS II的后仿真结果能够很好地满足时序要求,其中系统时钟(12.5MHz)最在能够满足20.59MHz,2MHz时钟能够满足41.03MHz。此结果在实际硬件测试中得到了验证。

5 实际产品性能分析

本文介绍的以太网/多路E1适配电路设计已实际应用在华环公司H0EL-1100 E1/100 Base-TX适配器中,表1是实际产品的吞吐量测试结果。由于以太网吞吐量包括IEEE802.3规定的导和SFD字节,而这部分信息是固定值,不需要经过E1信道传输到对端,所以测试值可能大于实际E1信道容量。表2是在8路E1配置下,以15MHz速率发包测得的以太网数据两端设备的传输延时。该设计在APEX II 20K100器件中占用的逻辑单元为3608个(共4160个逻辑门)。

在开发过程中由于采用高级硬件编程语言→编程器件的设计实现过程,大大缩短了开发周期,增加了硬件设计的灵活性和可移植性,也避免了专用集成电路设计的高风险。采用逻辑仿真与后时序仿真相结合的验证方法,基本可以保证设计的可靠性。基于上述优点,这种开发方式在中小指集成电路开发中已得到广泛的应用。尤其是近年来,硬件方面伴随着微电子工艺的迅速发展,编程器件的集成度正在成倍增长,越来越多的ASIC单元如微处理器、专用接口等嵌入编程器件中,使其适用范围更广;软件方面EDA开发商提供了众多的Ipcore及仿真工具,使得编程过程进一步简化,可靠性也不断增强;在此基础上SYS On Programmable Chip技术也开始走向商业化,为编程器件的发展提供了更为广阔的空间。

电路 VHDL FPGA 仿真 集成电路 电子 EDA 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)