HDTV接收机Viterbi译码器的FPGA实现

时间:08-31

来源:互联网

点击:

高清晰度数字电视(HDTV)技术是当今世界上最先进的图像压缩编码技术和数字通信技术的结合。它代表一个国的科技综合实力,蕴藏着巨大的市场潜力。数字电视地面广播编码正交频分复用(CMOFDM)传输系统以其较强的抗多径干扰性能、易于实现移动接收等优点在HDTV的研究中占有很重要的地位。而 COFDM系统中编、解码技术是影响系统性能的一个重要因素。本文正是基于一种最大似然译码——Viterbi(VB)译码算法思想,从FPGA实现的角度探讨在COFDM系统中内码(收缩卷积码)的解码。

1 设计算法简述

在HDTV 地面广播COFDM系统中,所用内码为收缩卷积码,除1/2主码率外,还有2/3。3/4、5/6、7/8码率的卷积编码。在实际的传输信道中,噪声一般是加性高斯白噪声(AWGN),输入AWGN信道的是二进制信号序列。为了充分利用信道输出信号的信息,提高传输系统译码

的可靠性,首先把信道的输出信号量化,将Q电平量化序列输入Viterbi译码器,因此本文采用的VB译码算法为软判决译码算法。

1.1 主码率1/2的卷积码编码

目前,在国际卫星通信和很多通信系统中,(2,1,6)码是首选的使用VB译码的标准卷积码。由于该码能使误码率达到最小,且能克服相位误差,所以在 HDTV地面广播COFDM传输系统中,内码采用(2,1,6)码,它的子生成元为(171,133),均为八进制。对应的生成多项式G(D)=[1+D +D2+D3+D6,1+D2+D3+D5+D6],df=10。其编码器的实现框图如图1。

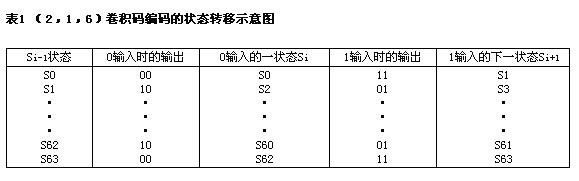

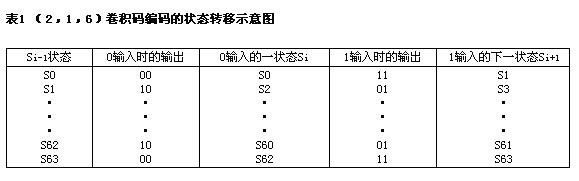

由于(2,1,6)码有62个状态,为直观直见,采用列表的方法来表述它的篱笆图,如表1所示。

1.2 收缩卷积码的实现

为了实现多码率传输,在提高码率的情况下不致使译码器的复杂性增加,在本设计中对(2,1,6)码进行增信删余(Puncctured)。如图1所示,在经上述编码后,对输出码字中的特定位置予以删除。这样右以产生码率为2/3、3/4、5/6、7/8的较高码率的卷积码。

1.3 维特比译码算法简述

Viterbi (VB)译码算法是一种最大似然译码算法。在收端的译码过程中,根据对接收码元处理方式的不同,分为硬判决和软判决译码。在同一译码算法下,虽然硬判决译码较软判决译码简单而易于实现,但在性能上要损失2~3dB。因此本文的FPGA实现是基于软判决来讨论的。具体算法如下:

(1)从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。对64态的每个状态,挑选并储存一条有最大度量的部分路径及部分度量值作为留选路径。

(2)j增加1,把此时刻进入每一状态的所有分支度量与同这些分支相加的前一时刻的留选路径的度量相加,得到此时刻进入每一状态的留选路径,加以存储并删去其它所有路径。

(3)为了FPGA设计中达到较高的时钟速度,本文在判决和输出路径寄存器的信息时,把所有64个路径寄存器的第一段信息元取出,按大数判决准则输出第一段信息元。

2 维特比译码的FPGA实现

本文是在Altera公司推出的Quartus电路仿真环境中,采用AHDL语言和原理图仿真结合的方法来完成VB译码器的FPGA实现。

2.1 译码器的整体实现方案

译码器的整个方案如图2所示。发端的数据径由信道传输过来,经过同步和信道估计,根据CSI信息对数据进行维特比量化,将量化后的信息解内交织后送入维特比解码单元。

接收到前端的码字后,首先须在发端的删除位置上填充特定的虚假码元,这一功能由Depuncture单元来完成。并由该单元产生量度计算禁止脉冲,送入主译码器,使译码器在译码时禁止对这些码元作量度计算。

主译码器的译码输出送到误码率监控单元,通过对误码率的统计来判定数据是否为同步接收,同时将该信息送入自同步监控单元,以供调整同步使用。当整个译码系统同步后,将输出一同步标识,表示系统已经同步,同时通过同步单元维持同步态。

2.2 译码器分模块的实现

2.2.1 R="1"/2的维特比译码模块

根据上述VB算法,对于一个软判决译码器,应具备以下几部分:

(1)度量值寄存器:用来存储各路径的度量值。其前级应有一状态发生器,产生64个状态和分支值。

(2)累加器、比较器和判决器。分别用来进行软距离的累加,比较各路径度量值的大小并选择输出信息元的值。

(3)路径寄存器:用来存储幸存路径。

模块设计如图3示。

分支度量值计算部分,首先根据接收的软判决信息计算出每一时刻各分支度量值,在Depuncture模块输出禁止脉冲的位置不能进行度量值运算。将该结果送入加比选电路,由表1所得的各状态间转移时的输出分别累加分支度量,并利用比较和选择电路得到留选路径,把此信息送入路径寄存器。当路径寄存器中64个状态的路径度量相等时,经过大数判决电路输出译码信息,送入下级的误码监控和自同步电路。

1 设计算法简述

在HDTV 地面广播COFDM系统中,所用内码为收缩卷积码,除1/2主码率外,还有2/3。3/4、5/6、7/8码率的卷积编码。在实际的传输信道中,噪声一般是加性高斯白噪声(AWGN),输入AWGN信道的是二进制信号序列。为了充分利用信道输出信号的信息,提高传输系统译码

的可靠性,首先把信道的输出信号量化,将Q电平量化序列输入Viterbi译码器,因此本文采用的VB译码算法为软判决译码算法。

1.1 主码率1/2的卷积码编码

目前,在国际卫星通信和很多通信系统中,(2,1,6)码是首选的使用VB译码的标准卷积码。由于该码能使误码率达到最小,且能克服相位误差,所以在 HDTV地面广播COFDM传输系统中,内码采用(2,1,6)码,它的子生成元为(171,133),均为八进制。对应的生成多项式G(D)=[1+D +D2+D3+D6,1+D2+D3+D5+D6],df=10。其编码器的实现框图如图1。

由于(2,1,6)码有62个状态,为直观直见,采用列表的方法来表述它的篱笆图,如表1所示。

1.2 收缩卷积码的实现

为了实现多码率传输,在提高码率的情况下不致使译码器的复杂性增加,在本设计中对(2,1,6)码进行增信删余(Puncctured)。如图1所示,在经上述编码后,对输出码字中的特定位置予以删除。这样右以产生码率为2/3、3/4、5/6、7/8的较高码率的卷积码。

1.3 维特比译码算法简述

Viterbi (VB)译码算法是一种最大似然译码算法。在收端的译码过程中,根据对接收码元处理方式的不同,分为硬判决和软判决译码。在同一译码算法下,虽然硬判决译码较软判决译码简单而易于实现,但在性能上要损失2~3dB。因此本文的FPGA实现是基于软判决来讨论的。具体算法如下:

(1)从某一时间单位j=m开始,对进入每一状态的所有长为j段分支的部分路径,计算部分路径度量。对64态的每个状态,挑选并储存一条有最大度量的部分路径及部分度量值作为留选路径。

(2)j增加1,把此时刻进入每一状态的所有分支度量与同这些分支相加的前一时刻的留选路径的度量相加,得到此时刻进入每一状态的留选路径,加以存储并删去其它所有路径。

(3)为了FPGA设计中达到较高的时钟速度,本文在判决和输出路径寄存器的信息时,把所有64个路径寄存器的第一段信息元取出,按大数判决准则输出第一段信息元。

2 维特比译码的FPGA实现

本文是在Altera公司推出的Quartus电路仿真环境中,采用AHDL语言和原理图仿真结合的方法来完成VB译码器的FPGA实现。

2.1 译码器的整体实现方案

译码器的整个方案如图2所示。发端的数据径由信道传输过来,经过同步和信道估计,根据CSI信息对数据进行维特比量化,将量化后的信息解内交织后送入维特比解码单元。

接收到前端的码字后,首先须在发端的删除位置上填充特定的虚假码元,这一功能由Depuncture单元来完成。并由该单元产生量度计算禁止脉冲,送入主译码器,使译码器在译码时禁止对这些码元作量度计算。

主译码器的译码输出送到误码率监控单元,通过对误码率的统计来判定数据是否为同步接收,同时将该信息送入自同步监控单元,以供调整同步使用。当整个译码系统同步后,将输出一同步标识,表示系统已经同步,同时通过同步单元维持同步态。

2.2 译码器分模块的实现

2.2.1 R="1"/2的维特比译码模块

根据上述VB算法,对于一个软判决译码器,应具备以下几部分:

(1)度量值寄存器:用来存储各路径的度量值。其前级应有一状态发生器,产生64个状态和分支值。

(2)累加器、比较器和判决器。分别用来进行软距离的累加,比较各路径度量值的大小并选择输出信息元的值。

(3)路径寄存器:用来存储幸存路径。

模块设计如图3示。

分支度量值计算部分,首先根据接收的软判决信息计算出每一时刻各分支度量值,在Depuncture模块输出禁止脉冲的位置不能进行度量值运算。将该结果送入加比选电路,由表1所得的各状态间转移时的输出分别累加分支度量,并利用比较和选择电路得到留选路径,把此信息送入路径寄存器。当路径寄存器中64个状态的路径度量相等时,经过大数判决电路输出译码信息,送入下级的误码监控和自同步电路。

数字电视 FPGA 编码器 Altera Quartus 电路 仿真 比较器 机顶盒 相关文章:

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 基于FPGA的MPEG-2复用器中FIFO的一种设计方案(07-22)

- 基于FPGA的数字电视CAS系统设计(07-24)

- 用CPLD和外部SRAM构成大容量FIFO的设计(07-29)

- 地面数字电视符号与载波同步的FPGA实现(08-01)

- 采用基于FPGA的SoC进行数字显示系统设计(08-05)