地面数字电视符号与载波同步的FPGA实现

时间:08-01

来源:互联网

点击:

4 仿真及分析

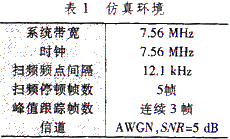

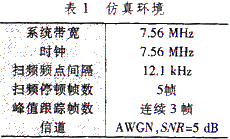

在FPGA平台上进行了基带模块的仿真以验证其功能。用于仿真的接收数据中加入了21.17 kHz的载波偏差。仿真的环境见表1。

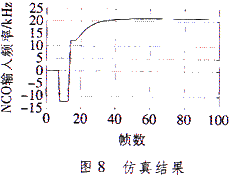

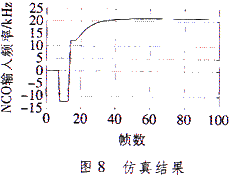

图8说明了仿真的结果,其中,纵坐标为NCO的输入频率,横坐标为经过的帧数。

从图8中可以看出,在同步模块工作的初期,由于载波偏差过大,相关模块无法找到相关峰。模块通过扫频、反馈环路与载波一般估计、精细估计的协同工作,跟踪载波频偏,同时扫频帧同步还获取了帧同步信息。由于硬件实现定点化计算精度有限,经过载波同步模块的信号仍然会有少量的载波频偏,这种偏差可通过后边的相位锁定或均衡器模块纠正。

对本文提出的同步模块架构通过FPGA实现并用Altera QuartusII软件进行了仿真和综合,资源的占用情况如表2。如果采用T/2或更高频率的系统时钟,帧头检测的相关器可以被I/Q两路复用,大大减少资源占用。由于算法简单,而且对数据的处理速度要求不高,因此该模块具有占用资源少、运行频率高等优点,完全满足国标系统接收机的设计要求。

5 小结

本文基于中国地面数字电视国家标准提出的系统结构,设计了接收机帧同步与载波同步的联合同步模块,并对硬件实现中可能遇到的问题进行了讨论。仿真证明,这种结构可有效解决帧同步与载波同步互相牵制的问题,准确获取帧头信息,且能对抗相对较大的载波频率偏差。如果采用较高的计算精度,载波频率跟踪的准确性则可以得到保证。

在FPGA平台上进行了基带模块的仿真以验证其功能。用于仿真的接收数据中加入了21.17 kHz的载波偏差。仿真的环境见表1。

图8说明了仿真的结果,其中,纵坐标为NCO的输入频率,横坐标为经过的帧数。

从图8中可以看出,在同步模块工作的初期,由于载波偏差过大,相关模块无法找到相关峰。模块通过扫频、反馈环路与载波一般估计、精细估计的协同工作,跟踪载波频偏,同时扫频帧同步还获取了帧同步信息。由于硬件实现定点化计算精度有限,经过载波同步模块的信号仍然会有少量的载波频偏,这种偏差可通过后边的相位锁定或均衡器模块纠正。

对本文提出的同步模块架构通过FPGA实现并用Altera QuartusII软件进行了仿真和综合,资源的占用情况如表2。如果采用T/2或更高频率的系统时钟,帧头检测的相关器可以被I/Q两路复用,大大减少资源占用。由于算法简单,而且对数据的处理速度要求不高,因此该模块具有占用资源少、运行频率高等优点,完全满足国标系统接收机的设计要求。

5 小结

本文基于中国地面数字电视国家标准提出的系统结构,设计了接收机帧同步与载波同步的联合同步模块,并对硬件实现中可能遇到的问题进行了讨论。仿真证明,这种结构可有效解决帧同步与载波同步互相牵制的问题,准确获取帧头信息,且能对抗相对较大的载波频率偏差。如果采用较高的计算精度,载波频率跟踪的准确性则可以得到保证。

数字电视 FPGA 振荡器 滤波器 仿真 Altera Quartus 相关文章:

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 基于FPGA的MPEG-2复用器中FIFO的一种设计方案(07-22)

- 基于FPGA的数字电视CAS系统设计(07-24)

- 用CPLD和外部SRAM构成大容量FIFO的设计(07-29)

- 采用基于FPGA的SoC进行数字显示系统设计(08-05)

- 用FPGA实现数字电视条件接收系统(09-01)