基于CPLD的智能宽带去边沿抖动技术

时间:07-24

来源:互联网

点击:

去开关信号抖动方法

去除数字信号引入和处理时出现的抖动常有以下三种途径:(1)RC滤波;(2)软件去抖动方法;(3)优化设计。

RC滤波是消除开关量器件抖动的最常见且有效的一种硬件方法,其实质与模拟处理方法中的单稳态触发器相似。比如,对键盘按键操作时,按键一般都会多次接触,常用的做法是加一个RC滤波电路,这样,只要设置的时常数大于抖动时间,即可有效消除抖动。软件去抖动方法一般是通过多次检测加上延时、比较来实现的。比如,对键盘按键操作时产生的抖动,可以多次检测,在一定的时间内是相同的键值则认为按下了一次,超过了一定的时间则认为有连续按键操作。

对于数字信号处理中(逻辑设计不合理)产生的抖动, 主要靠优化设计来解决。比如器件选择、同步设计、匹配终端等等。器件选择上,利用在频带、速度、精度等各方面相对实际需求有较大裕量的器件,这会使得信号受器件延时等影响造成的抖动大大减小。同步设计可以有效防止信号变化时出现的不必要的中间过程,一般是把异步设计的电路改成同步电路,这样各路信号经过几乎相同的时延,避免了中间过程变化引起的抖动。匹配终端的设计对于频率高端信号很有效。

智能宽带去抖动

提出的原因

由上面总结的方法知,几种方法都存在一定的不足。(1)利用了信号电平信息的去模拟抖动方法不能用于去除数字信号的抖动;(2)模拟去抖动方法中,平滑滤波的方法不能去除信号波动偏大时产生的抖动,而两个触发器解决办法则不能准确反应信号的正半周与负半周的比例,而且,对于单稳态触发器方法需要针对不同频率的信号采用不同的时间参数配置;(3)数字去抖动方法中,RC滤波方法只能针对慢变信号,因为快变信号将被滤除或附加一定的相移P时延,而软件设计的方法需要消耗大量的器件资源和时间资源,使得处理任务加重,这在有些时候是不容许的,对于优化设计则需要长期的经验才能有效避免。

总体上,上面的方法在每次设计时都将让我们权衡利用,效果有时也不尽人意。我们这里提出的智能宽带去抖动的方法可以解决大部分的问题,对模拟和数字信号产生的抖动均有效。由于是基于CPLD硬件的设计,方便改进,还可事先不必确切知道哪个IPO口输入的信号需要去抖动,同时不浪费其他硬件和软件资源。在实际应用中可以针对可能产生边沿抖动的所有信号进行去抖动处理,只要器件资源足够。

智能宽带去抖动原理

当我们需要进行较复杂的电路设计时,经常用到可编程器件,这样可以使得硬件软件化。实际使用时,可以针对引入的某个或几个信号进行去抖动处理,使设计得到简化。当信号输入CPLD时,首先进行去抖动处理,形成规范的脉冲波形后再进行后续信号处理。

无论是在模拟电路中还是在数字电路中形成的信号边沿的抖动,最终在送入CPLD的数字脉冲信号上都有相同的表现特征:紧跟在真实上(下)边沿后面有多个负(正)的虚假窄脉冲。因而在CPLD中我们可以采用相同的方法来进行边沿去抖动处理。由于信号频段不同,抖动时间也会不同,正确处理的前提条件:(1)信号边沿抖动时间小于信号周期的四分之一;(2)信号频率小于器件工作频率的八分之一。第一条是防止实际边沿界定不准,第二条是保证抖动范围可靠界定。对于频率未知情况,可以对频率进行分段,配合少量软件编程,针对信号频段可以进行智能分段处理。

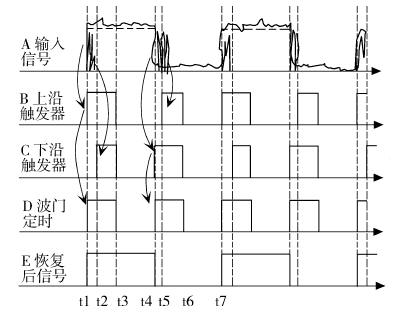

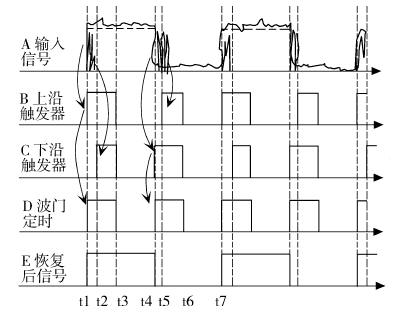

具体实现时,设置三个触发器:上升沿检测触发器B、下降沿触发器C以及波门定时触发器D。其中,上升沿触发器是在信号上升沿到来时变成高电平,下降沿触发器是在信号下降沿到来时变成高电平,抖动定时触发器当前两个触发器是在前两个触发器之一变成高电平时变成高电平。前两个触发器在抖动定时触发器清零时同时被清零,而抖动定时触发器清零时间由信号频率对应边沿抖动范围决定。时序如图4所示。其中,为观察方便,下降沿触发器变成高电平的时间拖后了一些。由图可见,输入信号在前后沿均有杂乱的毛刺,用常规方法消除这种抖动很困难,模拟去抖动方法无能为力,常规的数字方法需要消耗软件和硬件资源,而且容易形成误操作,用我们的方法就很简洁。

A信号第一次电平变化时(t1时刻),出现上升沿,B触发器开始触发,同时引发D触发器触发,第一次下降沿到来时(即第一个毛刺,t2时刻),C触发器触发,在设定定时范围内,三个触发器均保持不变。定时结束时(t3时刻),D触发器被清零,同时使B和C触发器清零。从上面可以看出来,只要t3时刻不超过t4时刻则不破坏原来信号的正负区间。

在A信号实际下降沿到来时刻(t4时刻),相当于定时触发器清零后第一次下降沿到来时刻,此时C触发器又受到触发,同时引发D触发器触发。B触发器在第一个毛刺到来时刻(t5时刻)得到触发,与前面相同。在这次定时没有结束前三个触发器变成不变,直到定时结束时刻(t6时刻),三个触发器同时被清零。余下依此类推。

图4 去抖动电路时序图

最后,我们来看一下D触发器波形,它在A信号正半周期间正负变化一次,在A信号负半周期间正负再变化一次,因此,只需用D触发器的上升沿来触发E信号,即可准确的恢复出没有抖动的A信号来,如图所示。如果A信号是周期信号,则E信号就是D信号的二分频信号(注意用信号本身与D信号来对齐正半周就行)。

上面是有信号边沿抖动的情况的分析,现在再来看看信号没有边沿抖动的情况。可以想象,在t2到t3时刻期间C触发器没有触发,但B和D触发器依然触发,因为A信号存在上升沿,在t5到t6时刻期间B触发器没有触发,但C和D触发器仍然触发,因为A信号在t4时刻存在下降沿,由此可以看出,在这种情况下,D触发器波形没有改变,从而可以用同样的方法得到E恢复信号。

当信号频率变化(或根本不是周期信号,只是一个个脉冲群)时,只要设置的波门定时范围满足前面提出的两个条件,则仍然可以适用。如果在多倍频程变化时,由于信号边沿抖动宽度不一致,低端的抖动范围可能已经超出了高频端周期的一半,不能进行准确还原,因此需要进行分段处理。在输入信号频率完全未知的情况下,可以实际测量参数,根据最稳定的情况来确定分段的界限和参数,如果配合少量的软件编程,提取信号稳定的段结果即可。这样,就可以在很宽的频带内,自动选择频段参数以正确进行去抖动处理。

去除数字信号引入和处理时出现的抖动常有以下三种途径:(1)RC滤波;(2)软件去抖动方法;(3)优化设计。

RC滤波是消除开关量器件抖动的最常见且有效的一种硬件方法,其实质与模拟处理方法中的单稳态触发器相似。比如,对键盘按键操作时,按键一般都会多次接触,常用的做法是加一个RC滤波电路,这样,只要设置的时常数大于抖动时间,即可有效消除抖动。软件去抖动方法一般是通过多次检测加上延时、比较来实现的。比如,对键盘按键操作时产生的抖动,可以多次检测,在一定的时间内是相同的键值则认为按下了一次,超过了一定的时间则认为有连续按键操作。

对于数字信号处理中(逻辑设计不合理)产生的抖动, 主要靠优化设计来解决。比如器件选择、同步设计、匹配终端等等。器件选择上,利用在频带、速度、精度等各方面相对实际需求有较大裕量的器件,这会使得信号受器件延时等影响造成的抖动大大减小。同步设计可以有效防止信号变化时出现的不必要的中间过程,一般是把异步设计的电路改成同步电路,这样各路信号经过几乎相同的时延,避免了中间过程变化引起的抖动。匹配终端的设计对于频率高端信号很有效。

智能宽带去抖动

提出的原因

由上面总结的方法知,几种方法都存在一定的不足。(1)利用了信号电平信息的去模拟抖动方法不能用于去除数字信号的抖动;(2)模拟去抖动方法中,平滑滤波的方法不能去除信号波动偏大时产生的抖动,而两个触发器解决办法则不能准确反应信号的正半周与负半周的比例,而且,对于单稳态触发器方法需要针对不同频率的信号采用不同的时间参数配置;(3)数字去抖动方法中,RC滤波方法只能针对慢变信号,因为快变信号将被滤除或附加一定的相移P时延,而软件设计的方法需要消耗大量的器件资源和时间资源,使得处理任务加重,这在有些时候是不容许的,对于优化设计则需要长期的经验才能有效避免。

总体上,上面的方法在每次设计时都将让我们权衡利用,效果有时也不尽人意。我们这里提出的智能宽带去抖动的方法可以解决大部分的问题,对模拟和数字信号产生的抖动均有效。由于是基于CPLD硬件的设计,方便改进,还可事先不必确切知道哪个IPO口输入的信号需要去抖动,同时不浪费其他硬件和软件资源。在实际应用中可以针对可能产生边沿抖动的所有信号进行去抖动处理,只要器件资源足够。

智能宽带去抖动原理

当我们需要进行较复杂的电路设计时,经常用到可编程器件,这样可以使得硬件软件化。实际使用时,可以针对引入的某个或几个信号进行去抖动处理,使设计得到简化。当信号输入CPLD时,首先进行去抖动处理,形成规范的脉冲波形后再进行后续信号处理。

无论是在模拟电路中还是在数字电路中形成的信号边沿的抖动,最终在送入CPLD的数字脉冲信号上都有相同的表现特征:紧跟在真实上(下)边沿后面有多个负(正)的虚假窄脉冲。因而在CPLD中我们可以采用相同的方法来进行边沿去抖动处理。由于信号频段不同,抖动时间也会不同,正确处理的前提条件:(1)信号边沿抖动时间小于信号周期的四分之一;(2)信号频率小于器件工作频率的八分之一。第一条是防止实际边沿界定不准,第二条是保证抖动范围可靠界定。对于频率未知情况,可以对频率进行分段,配合少量软件编程,针对信号频段可以进行智能分段处理。

具体实现时,设置三个触发器:上升沿检测触发器B、下降沿触发器C以及波门定时触发器D。其中,上升沿触发器是在信号上升沿到来时变成高电平,下降沿触发器是在信号下降沿到来时变成高电平,抖动定时触发器当前两个触发器是在前两个触发器之一变成高电平时变成高电平。前两个触发器在抖动定时触发器清零时同时被清零,而抖动定时触发器清零时间由信号频率对应边沿抖动范围决定。时序如图4所示。其中,为观察方便,下降沿触发器变成高电平的时间拖后了一些。由图可见,输入信号在前后沿均有杂乱的毛刺,用常规方法消除这种抖动很困难,模拟去抖动方法无能为力,常规的数字方法需要消耗软件和硬件资源,而且容易形成误操作,用我们的方法就很简洁。

A信号第一次电平变化时(t1时刻),出现上升沿,B触发器开始触发,同时引发D触发器触发,第一次下降沿到来时(即第一个毛刺,t2时刻),C触发器触发,在设定定时范围内,三个触发器均保持不变。定时结束时(t3时刻),D触发器被清零,同时使B和C触发器清零。从上面可以看出来,只要t3时刻不超过t4时刻则不破坏原来信号的正负区间。

在A信号实际下降沿到来时刻(t4时刻),相当于定时触发器清零后第一次下降沿到来时刻,此时C触发器又受到触发,同时引发D触发器触发。B触发器在第一个毛刺到来时刻(t5时刻)得到触发,与前面相同。在这次定时没有结束前三个触发器变成不变,直到定时结束时刻(t6时刻),三个触发器同时被清零。余下依此类推。

图4 去抖动电路时序图

最后,我们来看一下D触发器波形,它在A信号正半周期间正负变化一次,在A信号负半周期间正负再变化一次,因此,只需用D触发器的上升沿来触发E信号,即可准确的恢复出没有抖动的A信号来,如图所示。如果A信号是周期信号,则E信号就是D信号的二分频信号(注意用信号本身与D信号来对齐正半周就行)。

上面是有信号边沿抖动的情况的分析,现在再来看看信号没有边沿抖动的情况。可以想象,在t2到t3时刻期间C触发器没有触发,但B和D触发器依然触发,因为A信号存在上升沿,在t5到t6时刻期间B触发器没有触发,但C和D触发器仍然触发,因为A信号在t4时刻存在下降沿,由此可以看出,在这种情况下,D触发器波形没有改变,从而可以用同样的方法得到E恢复信号。

当信号频率变化(或根本不是周期信号,只是一个个脉冲群)时,只要设置的波门定时范围满足前面提出的两个条件,则仍然可以适用。如果在多倍频程变化时,由于信号边沿抖动宽度不一致,低端的抖动范围可能已经超出了高频端周期的一半,不能进行准确还原,因此需要进行分段处理。在输入信号频率完全未知的情况下,可以实际测量参数,根据最稳定的情况来确定分段的界限和参数,如果配合少量的软件编程,提取信号稳定的段结果即可。这样,就可以在很宽的频带内,自动选择频段参数以正确进行去抖动处理。

电子 CPLD 模拟电路 电路 开关电源 传感器 比较器 放大器 电压 继电器 电阻 电容 运算放大器 滤波器 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)