基于MCU+CPLD变压器测试系统的设计与实现

时间:07-21

来源:互联网

点击:

| 4.1 主要模块进程 | |

| 系统检测变压器时,MCU在正常初始化后,有键盘输入时会要求CPLD运行按键响应进程;CPLD根据所键入型号运行继电器控制进程,操作继电器板,并上传操作结果,MCU在认为前述操作正常后,才会要求CPLD启动对A/D控制的进程,模/数转换结果会送给MCU;MCU对转换结果进行处理后,又会要求CPLD运行显示进程,显示结果LCD上。 | |

| 4.2 仿真 | |

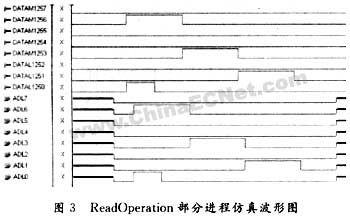

| 以读A/D结果(ReadOperation)进程为例进行仿真。 | |

| ——进程名称:ReadOperation | |

| ——敏感变量,RD | |

| ——输出变量,DataBusIn(送到数据总线上) | |

| ——目的:读操作 | |

| ReadOperation:process(RD,Enlcd,En125Low,En125High,CSIF,CSIM) | |

| 需要说明的是,信号变量在仿真时需声明其初始值,本读操作进程中的信号变量自会有其他进程(如片选进程)为其赋值,“&”作为连接运算符,可将多个对象或矢量连接成位数更大的矢量,对ReadOperation进程编译仿真的波形图如图3所示。 | |

| |

| 5 结语 | |

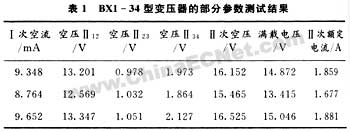

| 经过现场试用得到实验测试数据,表1列出3台BX1-34型变压器的部分参数测试结果,其中I次空流代表原边空载电流,空压II12指二次绕组1和2端的空载电压,其他类推,II次空压为二次绕组的总空载电压,满载电压指在二次绕组串接8Ω电阻时的电压值。 | |

| |

| [table] |

结果满足《信号维护规则)中对变压器“输入额定电压,二次端子电压空载时其误差不大于端子额定电压值的10%;容量为30-60VA的变压器满载时,其二次端子电压不小于端子额定电压值的85%”的规定。

本次开发综合考虑了MCU和CPLD的相互作用,采用了交流采样技术,认真考虑VHDL进程并行和CPLD的结构特点,并应用电路简化的几种技巧与方法,充分利用CPLD的硬件资源优化电路,实现系统对稳定性,精确度等方面的要求。

变压器 电流 电压 电阻 MCU CPLD LCD 电路 继电器 总线 单片机 滤波器 比较器 VHDL 仿真 相关文章:

- 基于CPLD的CCD信号发生器的研究(04-08)

- 现场可编程门阵列的供电(03-24)

- FPGA控制CLC5958型A/D转换器高速PCI采集(06-08)

- CPLD与绝对式编码器在高精度高速伺服单元中的应用(07-28)

- 微机保护控制接口装置的CPLD抗干扰设计(08-02)

- 基于FPGA的IRIG-B编码器的设计(08-20)