基于FPGA的高速大容量固态存储设备设计

时间:07-18

来源:互联网

点击:

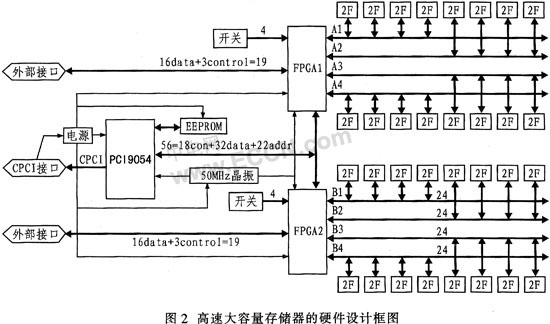

图2中2个外部接口连接2个A/D通道,采用两片FPGA作为控制和缓冲区,每片控制16组Flash。存储板通过PCI9054与CPCI总线相连,通过CPCI总线可以将存储板数据高速读回计算机。

3.2 系统设计思想

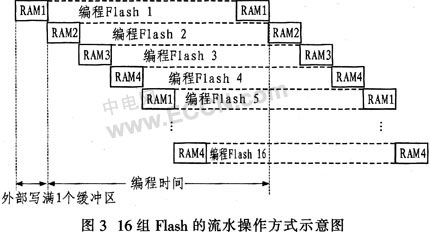

为了解决高速的数据采集和低速的Flash访问速度之间的矛盾,采取将数据流串并转换,复制多个操作模块并行处理的设计方法。通过利用FPGA内部的存储区实现4个双口RAM作为缓冲区。每条外部Flash总线用一个双口RAM,采集到的数据分时加载到4个RAM中,然后再写入Flash。写入Flash的操作以流水方式进行,具体方式如图3所示。首先,外部A/D采样通道写数据到RAM1。当RAM1写满时,加载数据到第一组Flash数据寄存器,加载完成后第一组Flash进入自动编程阶段;当RAM2写满时,第2组Flash加载开始,数据加载完成后,进入自动编程阶段。依次加载RAM3,当RAM4写满,第4组Flash开始加载后,FPGA内部控制重新写RAM1,开始对第5组Flash操作,然后依此循环方式对第6~16组Flash进行操作;当第16组数据加载完成后,第1组Flash已经编程结束,接着从第1组Flash开始加载和编程。可看出向16组Flash写入数据是并行的,通过并行写操作,可存储高速采集的数据。

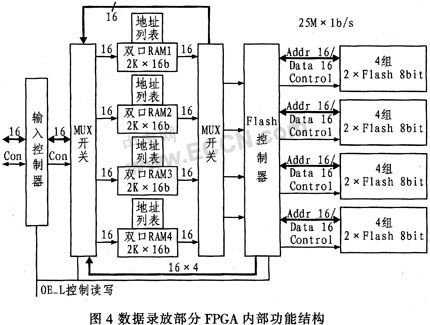

FPGA内部设计大体可划分为PCI9054操控部分和数据录放部分。PCI9054操控部分一方面跟PCI9054接口,一方面要完成对Flash的操作。数据录放部分主要完成外部数据写入、读出以及擦除、建立无产块信息列表等功能。由于对4组Flash的操作都是一样的,所以数据录放部分可以分为数据流控制部分和Flash操控部分。数据流控制部分控制数据写入或读取哪组Flash;Flash操控部分用于对Flash的具体操作。图4为数据录放部分FPGA功能结构。为了节省内部存储单元的数量,写入和读取数据要使用同样的缓存区。

3.3 无效块的建立和操作

当一个块中有一位或更多位不能正确操作时,就定义此块为无效块。无效块并不影响其他块的正常工作,各个块之间是相互独立的。所选的K9F2G08U0M在出厂时可能存在无效块,在使用中也可能产生新的无效块,但是器件的第一个块一定不是无效块。NAND Flash在出厂时就标记本身的无效块,每个块的第一页或第二页的空闲区的第一个数据不是FFh,则表示此块为无效块。为了保证Flash的正确操作,必须在操作之前建立无效块信息表。在每片FPGA中设计了4个2 048×1 bit的RAM用于存储无效块的信息。RAM的每一个存储单元存储相应总线上的4组Flash的无效块信息。其中某一块的无效块信息是4组Flash的无效块信息相“与”后的结果(1表示正常,0表示无效块)。在对Flash进行读、写或擦除操作之前,应先从RAM中读取无效块信息,然后根据无效块信息决定是否对当前块操作。

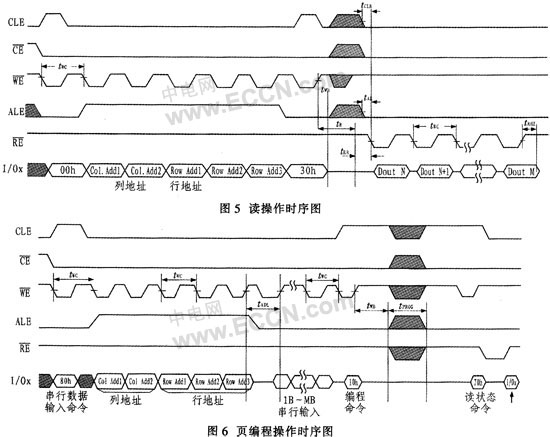

3.4 读写Flash操作

对Flash的读写操作都是基于页的,读写操作的时序分别如图5和图6所示。计算机通过CPCI总线发送出读或写命令后,FPGA内部根据接收到的命令执行相应操作。写Flash时,外部采集的数据输入RAM1,RAM1满后,开始向RAM2写入数据,同时选通第一条总线上第一组Flash的写模块,在写模块中通过计数器产生ALE、CLE、WE、RE等控制写Flash的相应时序,将数据从RAM中编程到Flash内存,并令页地址加1,依次循环(循环流程见图3)。当总线上的第4组Flash的页地址为64时,块地址加1,并读取无效块信息,如果为无效块,则屏蔽此块,重新读取下一块信息,直至读取到正常块为止。如果是正常块,则向此块中写入数据,同时将页地址清零。读操作与写操作类似,只不过是将Flash中的数据读出先送到RAM,然后依循环次序读取RAM即可。

3.5 PCI9054操控部分的设计

通过编写PCI9054专用的驱动和应用软件,实现由计算机通过CPCI总线操控存储板卡。在应用软件中,对Flash读写或者擦除等命令自定义为对CPCI总线发送特定的数据。而在FPGA内部根据PCI9054发送的局部端数据线上的特定数据判断是何种操作,并执行相应操作。FPGA和PCI9054通信的主要信号线有LHOLD、LHOLDA、READY、ADS、ADDR、DATA,利用这些信号线可以实现PCI9054局部端和FPGA握手。将数据写到计算机中。在PCI9054专用的驱动和应用软件中,利用DMA方式读取Flash,读取速度可提高至1.3 MHz×16 bit。

4 结束语

本设计采用流水、并行处理技术,利用FPGA内部嵌入的存储块设计一组高速数据缓冲区,使得多个慢速的存储器件并行工作,令系统内外部数据的速率匹配,避免了外置高速缓存,简化了硬件电路,且极大地提高了存储数据的速率。大容量高密度闪存器件可使单片存储板容量高达128 Gbit。在FP-GA内部设计中,建立Flash无效块信息列表,并在此基础上对Flash进行读、写、擦除及重建无效块信息等操作。使系统具有集成度高、灵活性好、可移植性强、速度快等特点。通过CPCI总线采取DMA方式读取,极大地提高了读取速度。当接收到的数据带宽很大,速度很高时,可将存储板并联起来,多个存储板级联可满足更大的存储容量需求,也可将级联并联二者结合起来以满足不同系统的要求。整个系统基于CPCI工控机箱,更适合于野外的工作环境,并能及时保存、分析数据。

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- 基于CPLD与单片机的高速数据采集系统(04-08)

- 在低成本FPGA中实现动态相位调整(03-25)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)

- SDH中E1接口分接复用器VHDL设计及FPGA实现(06-23)