基于FPGA的PCI总线接口设计

时间:06-11

来源:互联网

点击:

在现代数据采集及处理系统中,ISA、EISA、MCA等扩展总线已无法适应高速数据传输的要求,而PCI局部总线以其优异性价比和适应性成为大多数系统的主流总线。

PCI总线特点

PCI总线宽度32位,可升级到64位;最高工作频率33MHz,支持猝发工作方式,使传输速度更高;低随机访问延迟(对从总线上的主控寄存器到从属寄存器的写访问延迟为60ns);处理器/内存子系统能力完全一致;隐含的中央仲裁器;多路复用体系结构减少了管脚数和PCI部件;给于ISA、EISA、MAC系统的PCI扩展板,减少了用户的开发成本;对PCI扩展卡及元件能够自动配置,实现设备的即插即用;处理器独立,不依赖任何CPU,支持多种处理器及将来更高性能的处理器;支持64位地址;多主控制允许任何PCI主设备和从设备之间进行点对点访问;PCI提供数据和地址的奇偶校验功能,保证了数据的完整性和准确性。

PCI接口开发现状

目前开发PCI接口大体有两种方式,一是使用专用的PCI接口芯片,可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的用户接口。用户只要设计转换后的总线接口即可,缩短了开发周期,缺点是用户可能只用到部分PCI接口功能,这样造成了一定的逻辑资源浪费,也缺乏灵活性,很可能增加板上的组件,导致产品成本的增加和可靠性的降低。二是使用可编程器件,采用FPGA的优点在于其灵活的可编程性,首先PCI接口可以依据插卡功能进行最优化,而不必实现所有的PCI功能,这样可以节约系统的逻辑资源。而且,用户可以将PCI插卡上的其他用户逻辑与PCI接口逻辑集成在一个芯片上,实现紧凑的系统设计。当系统升级时,只需对可编程器件重新进行逻辑设计,而无需更新PCB版图。现在已经有越来越多的用户使用可编程器件如FPGA、CPLD等进行PCI设备的开发。

本文所论述的PCI接口控制器是作为一个转换接口工作于PCI总线与用户设备之间,也可以认为其主要功能是起一个桥梁作用,完成用户设备与PCI总线间的信息传送。

PCI接口设计

在PCI板卡的设计中,核心设计有时序控制和配置空间两部分。时序控制保证了板卡能按正常的PCI时序工作,配置空间部分保证了板卡的即插即用功能。在进行FPGA设计时本设计使用的软件是Altera的MAX+PLUSII,开发芯片是EPF10K20RC240-3。

● PCI接口配置空间的实现

PCI总线定义了3种物理地址空间,分别是存储器地址空间、I/O地址空间和配置地址空间。

配置空间是PCI所特有的一种空间,其目的在于提供一套适当的配置措施,使之满足现行的和可预见的系统配置机构。配置空间是一长度为256字节并且有特定记录结构的地址空间,可以在系统自举时访问,也可在其他时间访问。该空间分为首部区和设备有关区两部分,设备在每个区中只须实现必要的和与之相关的寄存器。配置空间的基地址寄存器提供了一种为设备指定存储空间或I/O空间的机制。操作系统在启动的时候要判断系统中有多少存储器、系统中的I/O设备需要多少地址空间,然后根据得到的结果,自动配置系统的存储空间和I/O空间,实现设备无关管理。在本设计中,那些只读的配置寄存器通过硬件连线到相应的值,因而不占用宏单元。通过配置寄存器,配置软件可了解目标设备的存在、功能及配置要求。

(1)厂商ID:此16位的只读寄存器定义了设备的生产厂商,可以使用MACH芯片最初的生产厂商-AMD公司的ID值1022。

(2)设备ID:该值由生产厂商分配以识别其产品,可为除00000000H和0FFFFFFFFH中的任意值。

(3)命令寄存器:此寄存器控制了设备响应PCI访问的能力。位1、6、8在本设计中被实现。本设计要求实现对存储空间的访问,位1设置为1,则设备响应PCI对存储器访问;位6控制了设备对奇偶校验错误的响应;当位8被设置为1时,设备能够驱动SERR线,0则禁止设备的SERR输出驱动器。在这里当系统复位后,位1、6、8被设置为0。

(4)状态寄存器:此寄存器记录了PCI相关事件的信息。在本系统中,位9、10、11、14、15被设计实现。位10∶9为设备选择(DEVSEL#)定时,00B为慢速,01B为中速,10B为快速,11B保留。本设计这两位被硬件连线为01B。当目标设备失败时,位11被设置为1,当发生系统错误时位14置1,发生奇偶校验错误时位15置1。

(5)基地址寄存器:该寄存器用来映射设备的存储器地址空间,与设备地址空间大小相应的低位被强制为0,因此在配置写交易中,配置软件通过对这个寄存器的所有位写1,然后再读出该寄存器的值来决定设备存储器所占用的地址范围。位0用来定义设备是存储器映射还是I/O映射,在本设计中,位0被设为低以表明目标设备为存储器映射的。

如需要256字节的存储空间,配置软件写入0FFFFFFFFH,本设备送出0FFFFFF00H,而配置软件再次写入基地址寄存器的值与本设备的0FFFFFF00H相与的结果就是基地址值,如配置软件再次写入0CD000000H则基地址值为0CD000000H。

(6)类代码寄存器:这个24位的只读寄存器用来说明设备的基本功能和它的可编程接口。这里,此寄存器被强制为018000H,即设备为大容量存储控制器。

(7)首部类型寄存器:这个只读寄存器的位0~6定义了首部格式,位7说明了设备为单功能还是多功能。首部类型1为PCI-PCI桥定义,首部类型2则用于PCI CardBus桥。在本设计中寄存器被强制为0来显示其为单功能设备且首部类型为0。

● 时序控制

在时序控制程序中采用状态机模型来实现不同时序的转换。各种命令、数据交换、控制均在状态机的管理下进行工作。PCI总线上的信号是并行工作的,因此,对应每个状态必须明确其执行的任务。这些任务要用VHDL的进程语句来描述所发生的事件。本设计中的状态机共使用了6种状态,它以从设备响应状况为依据,主要以DEVSEL#信号和TRDY#信号的状况为依据。状态机如图1所示,分别对应空闲状态(此状态DEVSEL#、TRDY#和STOP#以及其他输出信号为高阻态);准备状态、DEVSEL#和TRDY#均为高电平状态,DEVSEL#为低电平且TRDY#为高电平状态,DEVSEL#和TRDY#均为低电平状态;操作结束状态(此状态使DEVSEL#、TRDY#和STOP#维持一个周期高电平)。本系统接到复位信号后对系统进行复位,然后转入空闲状态,在空闲状态中采样总线,并根据总线的变化来决定下一个时钟上升沿后状态机转入何种状态,这些时序和程序中用到的信号都是基本且必须的,在进行开发时可以根据需要增添必要的状态和信号,VHDL对状态机的描述如下。

type pci_state is (Idle, Ready, DevTrdyHi, DevLoTrdyHi, DevTrdyLo, OprOver);

signal c_state :pci_state;

Idle为空闲状态;Ready为准备状态;DevTrdyHi表示DEVSEL#和TRDY#均为高电平状态;DevLoTrdyHi表示DEVSEL#为低电平且TRDY#为高电平状态;DevTrdyLo表示DEVSEL#和TRDY#均为低电平状态;OprOverr表示操作结束状态。

程序如下。

process(pci_rst,pci_clk)

begin

if pci_rst = '0' then

c_state <= Idle;

elsif pci_clk'event and pci_clk='1' then

case c_state is

when Idle=>

if pci_FRAME_l='1' and pci_irdy_l='1' then

c_state <= Idle;

elsif pci_frame_l='0' then

c_state <= Ready;

else

c_state <= c_state;

end if;

when Ready=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

else

c_state <= DevTrdyHi;

end if;

when DevTrdyHi=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

else

c_state <= DevLoTrdyHi;

end if;

when DevLoTrdyHi=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

else

c_state <= DevTrdyLo;

end if;

when DevTrdyLo=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

elsif pci_frame_l='1' and pci_irdy_l='0' and trdy_l='0' then

c_state <= OprOver;

else

c_state <= c_state;

end if;

when OprOver=>

c_state <= Idle;

when others=>

c_state <= Idle;

end case;

end if;

end process;

下一步应列出每个状态所对应的并发事件,写出相关的进程。进程语句是一个并行语句,它定义进程被激活时将要执行的特定行为。例如,在Ready状态时,就要判断从主设备方发来的地址信息是否与从设备地址相同,因此要写出地址比较进程。

address_compare:process(pci_rst,pci_clk),主要内容是对地址译码,判断地址是否在从设备空间,如果在此空间则可做下一步动作,否则不做其他动作。

从以上分析过程可以得到整个设计思路如下:在时钟的上升沿采样FRAME#、地址和命令,如果FRAME#有效则译码地址和命令,如果总线命令为011x,并且总线上的地址在目标地址范围内,表明这是对本设备的存储器操作;或者总线命令为101x,且IDSEL信号有效,表明这是对本设备配置空间的操作。在这两种情况下,根据总线命令的最后一位确定是读操作还是写操作,有效DEVSEL#和TRDY#信号,开始数据传输;并在传输过程中采样FRAME#和IRDY#信号,确认最后一个数据周期,无效DEVSEL#和TRDY#信号,结束数据传输。

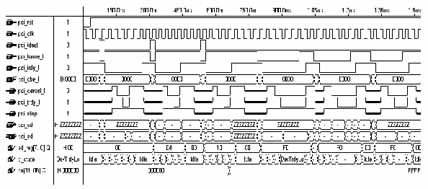

通过以上设计,在MAX+PLUSII环境下的其中一组模拟结果如图2所示。

PCI总线特点

PCI总线宽度32位,可升级到64位;最高工作频率33MHz,支持猝发工作方式,使传输速度更高;低随机访问延迟(对从总线上的主控寄存器到从属寄存器的写访问延迟为60ns);处理器/内存子系统能力完全一致;隐含的中央仲裁器;多路复用体系结构减少了管脚数和PCI部件;给于ISA、EISA、MAC系统的PCI扩展板,减少了用户的开发成本;对PCI扩展卡及元件能够自动配置,实现设备的即插即用;处理器独立,不依赖任何CPU,支持多种处理器及将来更高性能的处理器;支持64位地址;多主控制允许任何PCI主设备和从设备之间进行点对点访问;PCI提供数据和地址的奇偶校验功能,保证了数据的完整性和准确性。

PCI接口开发现状

目前开发PCI接口大体有两种方式,一是使用专用的PCI接口芯片,可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的用户接口。用户只要设计转换后的总线接口即可,缩短了开发周期,缺点是用户可能只用到部分PCI接口功能,这样造成了一定的逻辑资源浪费,也缺乏灵活性,很可能增加板上的组件,导致产品成本的增加和可靠性的降低。二是使用可编程器件,采用FPGA的优点在于其灵活的可编程性,首先PCI接口可以依据插卡功能进行最优化,而不必实现所有的PCI功能,这样可以节约系统的逻辑资源。而且,用户可以将PCI插卡上的其他用户逻辑与PCI接口逻辑集成在一个芯片上,实现紧凑的系统设计。当系统升级时,只需对可编程器件重新进行逻辑设计,而无需更新PCB版图。现在已经有越来越多的用户使用可编程器件如FPGA、CPLD等进行PCI设备的开发。

本文所论述的PCI接口控制器是作为一个转换接口工作于PCI总线与用户设备之间,也可以认为其主要功能是起一个桥梁作用,完成用户设备与PCI总线间的信息传送。

PCI接口设计

在PCI板卡的设计中,核心设计有时序控制和配置空间两部分。时序控制保证了板卡能按正常的PCI时序工作,配置空间部分保证了板卡的即插即用功能。在进行FPGA设计时本设计使用的软件是Altera的MAX+PLUSII,开发芯片是EPF10K20RC240-3。

● PCI接口配置空间的实现

PCI总线定义了3种物理地址空间,分别是存储器地址空间、I/O地址空间和配置地址空间。

配置空间是PCI所特有的一种空间,其目的在于提供一套适当的配置措施,使之满足现行的和可预见的系统配置机构。配置空间是一长度为256字节并且有特定记录结构的地址空间,可以在系统自举时访问,也可在其他时间访问。该空间分为首部区和设备有关区两部分,设备在每个区中只须实现必要的和与之相关的寄存器。配置空间的基地址寄存器提供了一种为设备指定存储空间或I/O空间的机制。操作系统在启动的时候要判断系统中有多少存储器、系统中的I/O设备需要多少地址空间,然后根据得到的结果,自动配置系统的存储空间和I/O空间,实现设备无关管理。在本设计中,那些只读的配置寄存器通过硬件连线到相应的值,因而不占用宏单元。通过配置寄存器,配置软件可了解目标设备的存在、功能及配置要求。

(1)厂商ID:此16位的只读寄存器定义了设备的生产厂商,可以使用MACH芯片最初的生产厂商-AMD公司的ID值1022。

(2)设备ID:该值由生产厂商分配以识别其产品,可为除00000000H和0FFFFFFFFH中的任意值。

(3)命令寄存器:此寄存器控制了设备响应PCI访问的能力。位1、6、8在本设计中被实现。本设计要求实现对存储空间的访问,位1设置为1,则设备响应PCI对存储器访问;位6控制了设备对奇偶校验错误的响应;当位8被设置为1时,设备能够驱动SERR线,0则禁止设备的SERR输出驱动器。在这里当系统复位后,位1、6、8被设置为0。

(4)状态寄存器:此寄存器记录了PCI相关事件的信息。在本系统中,位9、10、11、14、15被设计实现。位10∶9为设备选择(DEVSEL#)定时,00B为慢速,01B为中速,10B为快速,11B保留。本设计这两位被硬件连线为01B。当目标设备失败时,位11被设置为1,当发生系统错误时位14置1,发生奇偶校验错误时位15置1。

(5)基地址寄存器:该寄存器用来映射设备的存储器地址空间,与设备地址空间大小相应的低位被强制为0,因此在配置写交易中,配置软件通过对这个寄存器的所有位写1,然后再读出该寄存器的值来决定设备存储器所占用的地址范围。位0用来定义设备是存储器映射还是I/O映射,在本设计中,位0被设为低以表明目标设备为存储器映射的。

如需要256字节的存储空间,配置软件写入0FFFFFFFFH,本设备送出0FFFFFF00H,而配置软件再次写入基地址寄存器的值与本设备的0FFFFFF00H相与的结果就是基地址值,如配置软件再次写入0CD000000H则基地址值为0CD000000H。

(6)类代码寄存器:这个24位的只读寄存器用来说明设备的基本功能和它的可编程接口。这里,此寄存器被强制为018000H,即设备为大容量存储控制器。

(7)首部类型寄存器:这个只读寄存器的位0~6定义了首部格式,位7说明了设备为单功能还是多功能。首部类型1为PCI-PCI桥定义,首部类型2则用于PCI CardBus桥。在本设计中寄存器被强制为0来显示其为单功能设备且首部类型为0。

● 时序控制

在时序控制程序中采用状态机模型来实现不同时序的转换。各种命令、数据交换、控制均在状态机的管理下进行工作。PCI总线上的信号是并行工作的,因此,对应每个状态必须明确其执行的任务。这些任务要用VHDL的进程语句来描述所发生的事件。本设计中的状态机共使用了6种状态,它以从设备响应状况为依据,主要以DEVSEL#信号和TRDY#信号的状况为依据。状态机如图1所示,分别对应空闲状态(此状态DEVSEL#、TRDY#和STOP#以及其他输出信号为高阻态);准备状态、DEVSEL#和TRDY#均为高电平状态,DEVSEL#为低电平且TRDY#为高电平状态,DEVSEL#和TRDY#均为低电平状态;操作结束状态(此状态使DEVSEL#、TRDY#和STOP#维持一个周期高电平)。本系统接到复位信号后对系统进行复位,然后转入空闲状态,在空闲状态中采样总线,并根据总线的变化来决定下一个时钟上升沿后状态机转入何种状态,这些时序和程序中用到的信号都是基本且必须的,在进行开发时可以根据需要增添必要的状态和信号,VHDL对状态机的描述如下。

type pci_state is (Idle, Ready, DevTrdyHi, DevLoTrdyHi, DevTrdyLo, OprOver);

signal c_state :pci_state;

Idle为空闲状态;Ready为准备状态;DevTrdyHi表示DEVSEL#和TRDY#均为高电平状态;DevLoTrdyHi表示DEVSEL#为低电平且TRDY#为高电平状态;DevTrdyLo表示DEVSEL#和TRDY#均为低电平状态;OprOverr表示操作结束状态。

程序如下。

process(pci_rst,pci_clk)

begin

if pci_rst = '0' then

c_state <= Idle;

elsif pci_clk'event and pci_clk='1' then

case c_state is

when Idle=>

if pci_FRAME_l='1' and pci_irdy_l='1' then

c_state <= Idle;

elsif pci_frame_l='0' then

c_state <= Ready;

else

c_state <= c_state;

end if;

when Ready=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

else

c_state <= DevTrdyHi;

end if;

when DevTrdyHi=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

else

c_state <= DevLoTrdyHi;

end if;

when DevLoTrdyHi=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

else

c_state <= DevTrdyLo;

end if;

when DevTrdyLo=>

if pci_frame_l='1' and pci_irdy_l='1' then

c_state <= OprOver;

elsif pci_frame_l='1' and pci_irdy_l='0' and trdy_l='0' then

c_state <= OprOver;

else

c_state <= c_state;

end if;

when OprOver=>

c_state <= Idle;

when others=>

c_state <= Idle;

end case;

end if;

end process;

下一步应列出每个状态所对应的并发事件,写出相关的进程。进程语句是一个并行语句,它定义进程被激活时将要执行的特定行为。例如,在Ready状态时,就要判断从主设备方发来的地址信息是否与从设备地址相同,因此要写出地址比较进程。

address_compare:process(pci_rst,pci_clk),主要内容是对地址译码,判断地址是否在从设备空间,如果在此空间则可做下一步动作,否则不做其他动作。

从以上分析过程可以得到整个设计思路如下:在时钟的上升沿采样FRAME#、地址和命令,如果FRAME#有效则译码地址和命令,如果总线命令为011x,并且总线上的地址在目标地址范围内,表明这是对本设备的存储器操作;或者总线命令为101x,且IDSEL信号有效,表明这是对本设备配置空间的操作。在这两种情况下,根据总线命令的最后一位确定是读操作还是写操作,有效DEVSEL#和TRDY#信号,开始数据传输;并在传输过程中采样FRAME#和IRDY#信号,确认最后一个数据周期,无效DEVSEL#和TRDY#信号,结束数据传输。

通过以上设计,在MAX+PLUSII环境下的其中一组模拟结果如图2所示。

总线 FPGA PCB CPLD Altera VHDL 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)