基于FPGA的远程图像采集系统设计

时间:11-23

来源:互联网

点击:

组帧状态机

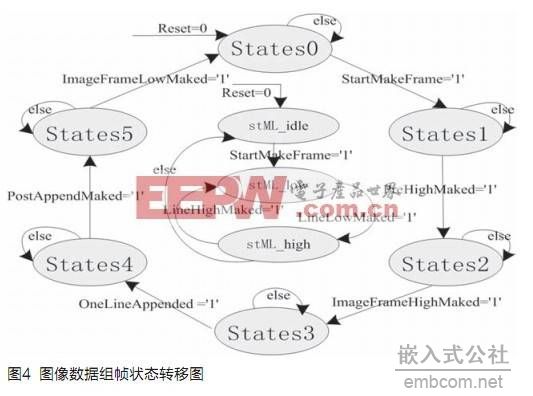

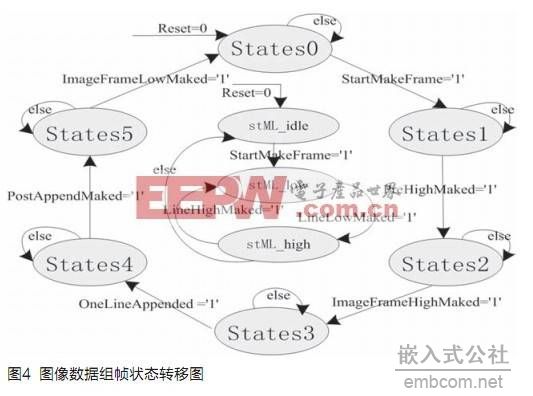

状态机在FPGA内部设计成两部分,为组帧状态机(外圈)和组行状态机(内圈)。其中组帧状态机各状态转移顺序及条件见图4,各状态占用时间可以通过组行状态机中的行计数来控制,近而可以完成不同大小规格的图像的接收。组帧状态机共有6个状态。

state0:空闲状态(系统复位)。state1:帧有效期开始到行有效期开始之间的延时。state2:图像帧有效期,state3:图像参数帧有效期。state4:行有效期结束到帧有效期结束之间的延时。state5:帧无效期。Reset为输入的状态机复位信号,在系统复位状态,如果用来启动状态机的信号StartMakeFrame = 1,状态机开始工作,进入系统下一状态,组帧状态机在各状态转移条件满足时,依次进入下一状态,否则,保持在原状态。

组行状态机共有3个状态。

stML_Idle:空闲状态。stML_High:行有效期。stML_Low:行无效期。在外圈组帧状态机的每个状态中,包含n个组行状态,所包含的组行状态机中的行数即组帧状态机各状态所占用时间,组行状态机和组帧状态机启动条件一致,同时启动。

以采集可见光图像数据为例,上电复位期间系统处于states0状态,状态机用外部输入的7.375MHz时钟同步整个运行过程,图像的帧、行、图像数据等信号在同步时钟的下降沿跳变,上升沿锁存。一帧图像数据的大小为512×512bit,并将图像附带的参数信息写入图像数据后一行(即513行),在帧有效期间(states1、 states2、 states3状态),CLK 信号作为行计数器的时钟,每帧图像在行有效之前有1行无效图像信号(states1), 在states2状态下,控制采集一帧中的前512行,在states3状态下,采集图象的参数信息,将图像数据和状态参数组合为统一的数据帧,采集完一帧图像数据后等待下一个帧同步信号的到来。在行有效期(stML_High)控制采集一行中的512个像素点数据,在CLK信号的上升沿进行计数, 在数据有效期间采集完512个像素点,等待下一个行同步信号的到来,按同样方式对下一行512像素点数据进行采集,直至采集完一帧中的512行。

系统仿真

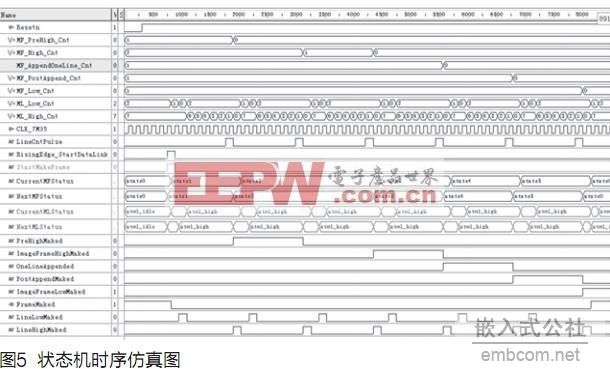

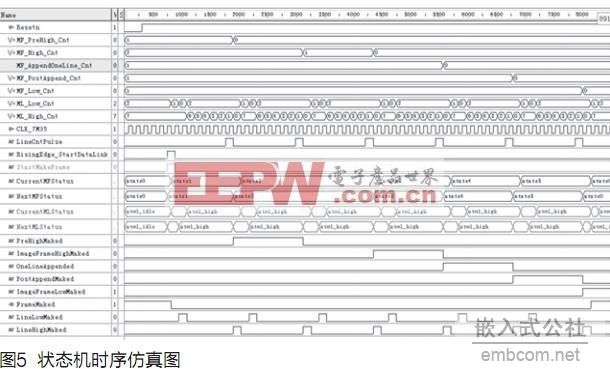

在该系统中,状态机设计是难点,图5是运用Active-HDL7.1仿真工具的状态机仿真结果,仿真时,采用7.375MHz时钟同步,状态机启动后,计数寄存器里的数据递减,进而产生各状态转移满足的条件,以此实现状态机的翻转。

在Active-HDL7.1中编写TestBench文件时,通过向组帧状态机计数寄存器写数,来控制各状态所占用的时间,利用 StartMakeFrame信号高电平启动状态机,各状态发生翻转时,状态完成标志就产生产生高电平跳变。

根据图5的仿真结果,可以看出组帧状态机工作正常,所有的逻辑关系也都验证无误。

结语

本文采用FPGA设计实现高速图像采集系统,并采用LVDS接口实现接收与发送,各种模块之间通过缓存实现通信,避免图像的丢失;采集的图像类型和图像尺寸可以通过软件重新配置FPGA进行调整。总之,基于FPGA 的高速专用图像采集系统电路集成度高、信噪比高、功耗低、成本低、速度快以及接口方便,所设计系统采用两帧切换存储方式,使得后续的其它图像处理模块能够与图像采集模块并行工作,为图像处理器的高度集成化实现提供了可能性。

参考文献:

[1] 侯伯亨, 顾新. VHDL硬件描述语言与数字逻辑电路设计[M]. 西安:电子科技大学出版社, 2003

[2] LVDS Ower’sManual ( 2nd Edition) [R]. National Semiconductor, 2000

[3] Application note 3806,Performance Test for a Senrializer and Deserializer Pair:MAX9247 and MAX9218[R]. Maxim IC,2006

[4] 孙航. Kilinx可编程逻辑器件的高级应用与设计技巧[M]. 北京: 电子工业出版社, 2004

[5] 王诚, 薛小刚, 钟信潮. Xilinx ISE使用详解[M]. 人民邮电出版社, 2005

[6] IDT72V2103 datasheet[R], IDT 2001

状态机在FPGA内部设计成两部分,为组帧状态机(外圈)和组行状态机(内圈)。其中组帧状态机各状态转移顺序及条件见图4,各状态占用时间可以通过组行状态机中的行计数来控制,近而可以完成不同大小规格的图像的接收。组帧状态机共有6个状态。

state0:空闲状态(系统复位)。state1:帧有效期开始到行有效期开始之间的延时。state2:图像帧有效期,state3:图像参数帧有效期。state4:行有效期结束到帧有效期结束之间的延时。state5:帧无效期。Reset为输入的状态机复位信号,在系统复位状态,如果用来启动状态机的信号StartMakeFrame = 1,状态机开始工作,进入系统下一状态,组帧状态机在各状态转移条件满足时,依次进入下一状态,否则,保持在原状态。

组行状态机共有3个状态。

stML_Idle:空闲状态。stML_High:行有效期。stML_Low:行无效期。在外圈组帧状态机的每个状态中,包含n个组行状态,所包含的组行状态机中的行数即组帧状态机各状态所占用时间,组行状态机和组帧状态机启动条件一致,同时启动。

以采集可见光图像数据为例,上电复位期间系统处于states0状态,状态机用外部输入的7.375MHz时钟同步整个运行过程,图像的帧、行、图像数据等信号在同步时钟的下降沿跳变,上升沿锁存。一帧图像数据的大小为512×512bit,并将图像附带的参数信息写入图像数据后一行(即513行),在帧有效期间(states1、 states2、 states3状态),CLK 信号作为行计数器的时钟,每帧图像在行有效之前有1行无效图像信号(states1), 在states2状态下,控制采集一帧中的前512行,在states3状态下,采集图象的参数信息,将图像数据和状态参数组合为统一的数据帧,采集完一帧图像数据后等待下一个帧同步信号的到来。在行有效期(stML_High)控制采集一行中的512个像素点数据,在CLK信号的上升沿进行计数, 在数据有效期间采集完512个像素点,等待下一个行同步信号的到来,按同样方式对下一行512像素点数据进行采集,直至采集完一帧中的512行。

系统仿真

在该系统中,状态机设计是难点,图5是运用Active-HDL7.1仿真工具的状态机仿真结果,仿真时,采用7.375MHz时钟同步,状态机启动后,计数寄存器里的数据递减,进而产生各状态转移满足的条件,以此实现状态机的翻转。

在Active-HDL7.1中编写TestBench文件时,通过向组帧状态机计数寄存器写数,来控制各状态所占用的时间,利用 StartMakeFrame信号高电平启动状态机,各状态发生翻转时,状态完成标志就产生产生高电平跳变。

根据图5的仿真结果,可以看出组帧状态机工作正常,所有的逻辑关系也都验证无误。

结语

本文采用FPGA设计实现高速图像采集系统,并采用LVDS接口实现接收与发送,各种模块之间通过缓存实现通信,避免图像的丢失;采集的图像类型和图像尺寸可以通过软件重新配置FPGA进行调整。总之,基于FPGA 的高速专用图像采集系统电路集成度高、信噪比高、功耗低、成本低、速度快以及接口方便,所设计系统采用两帧切换存储方式,使得后续的其它图像处理模块能够与图像采集模块并行工作,为图像处理器的高度集成化实现提供了可能性。

参考文献:

[1] 侯伯亨, 顾新. VHDL硬件描述语言与数字逻辑电路设计[M]. 西安:电子科技大学出版社, 2003

[2] LVDS Ower’sManual ( 2nd Edition) [R]. National Semiconductor, 2000

[3] Application note 3806,Performance Test for a Senrializer and Deserializer Pair:MAX9247 and MAX9218[R]. Maxim IC,2006

[4] 孙航. Kilinx可编程逻辑器件的高级应用与设计技巧[M]. 北京: 电子工业出版社, 2004

[5] 王诚, 薛小刚, 钟信潮. Xilinx ISE使用详解[M]. 人民邮电出版社, 2005

[6] IDT72V2103 datasheet[R], IDT 2001

电子 FPGA 电路 红外 Xilinx IDT 仿真 VHDL Maxim 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)