用FPGA实现音频采样率的转换

时间:02-07

来源:互联网

点击:

设计实现

可以在Simulink中用Synplify DSP模块集和Simulink的滤波器设计与分析(FDA)工具实现该电路。FDA工具可帮助生成和验证各种FIR和IIR滤波器。该工具是Simulink信号处理工具箱的组成部分,Synplify DSP就是使用此工具箱实现滤波器结构。

Synplify DSP模块集或FDA工具提供的所有电路元件在PortIN和PortOUT描述之间都有定义,它们能够生成VHDL或Verilog代码。 Simulink模块集中的FFT和SCOPE元件对动态响应进行频谱分析和验证。这些模块专门用于功能验证,包括浮点到定点转换功能(量化)。这些模块都不用硬件实现。

算法实现的第一部分包括两个FIR滤波器:第一个滤波器有512个抽头,第二个滤波器有6?个抽头。因此,由过采样生成的RTL代码共含有576个乘法运算,这正是使用FPGA显得并不具有商业可行性的原因。这么大的FPGA会受到成本制约,因为需要用到有 6?0个DSP48模块的特大型Xilinx Virtex-5 XC5VSX95T器件。

未映射到专用硬件结构(DSP模块)的所有乘法运算都必须用通用逻辑资源(LUT或寄存器)构建。这样会导致资源要求上升而最高时钟速度下降。与通用逻辑单元相比,专用的DSP48模块作为乘法器会有效得多(图4)。

图4:用Simulink的滤波器设计与分析(FDA)工具实现滤波器。

设计优化

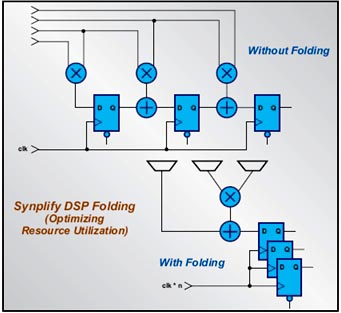

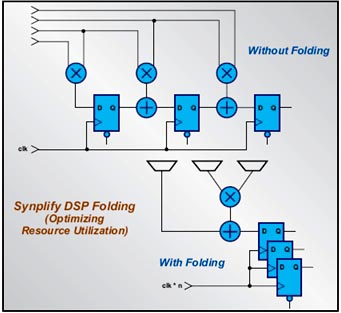

Synplify DSP的折叠选项可用来尽量减少所用乘法器的数量。在低采样频率下工作的电路尤其可从这一优化中受益。

其原理很简单。通常,每个乘法运算使用一个硬件乘法器,即使对于千赫级采样频率也是如此。然而,FPGA能以数百兆赫级的时钟速度工作。如果硬件乘法器在FPGA的系统频率下工作,就可以用时间多路复用过程按时序处理乘法运算。

假设电路的采样频率是3MHz,而FPGA最高可以在120MHz频率下运行。如果以系统频率运行乘法器,则每个硬件乘法器可以执行40次运算。此时所需硬件可以减少40倍。也就是说可以将上述采样率转换器(或使用低采样频率的任何其他电路)“折叠”到仅需要很少硬件乘法器的程度。所以,也可以在现有最小的低成本FPGA中实现这种转换器,从而真正取代DSP。

当然,还可能将计算量特别大的算法从DSP卸载到FPGA,从而减轻处理器的负荷。如果您的DSP应用已经超过性能极限,而且您已经为针对特定DSP架构的应用源代码作出大量投入,那么这种方法尤其有用(图5)。

图5:可以用折叠功能显著减少所需的FPGA资源。

因为Synplify DSP中的折叠功能还支持多速率系统,所以与只有一种采样频率的系统相比,您可以进一步减少所需乘法器的数量。过采样使用两个FIR滤波器完成。这两个滤波器以不同的采样频率运行。以较高采样频率运行的滤波器可以用您指定的折叠系数进行折叠。

以较低采样频率运行的滤波器用相对较高的系数折叠。获得此系数的方法是用两个滤波器的采样频率之差乘以折叠系数。例如,如果一个滤波器的采样频率是另一滤波器的8倍,则较快的滤波器用系数 8折叠,而较慢的滤波器用系数6?折叠。

这样甚至可能生成以通常不能折叠的很高采样率运行的空间优化电路。例如,如果系统以 200MHz采样率运行并使用折叠系数2,那么系统频率就可以提高到400MHz。

您还可以将折叠系数定义为1。以最高采样率运行的电路元件不折叠。但是,以较低采样频率运行的多速率系统的所有电路元件都可从折叠和空间优化实现中受益。您只需将系统作为整体为其定义折叠系数即可。然后,折叠会自动传播到所有采样频率。

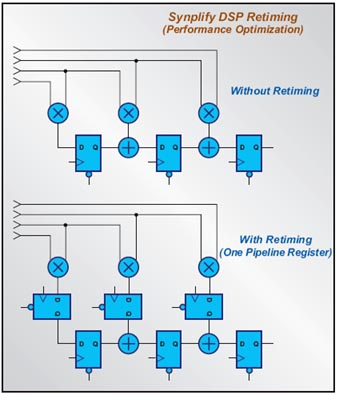

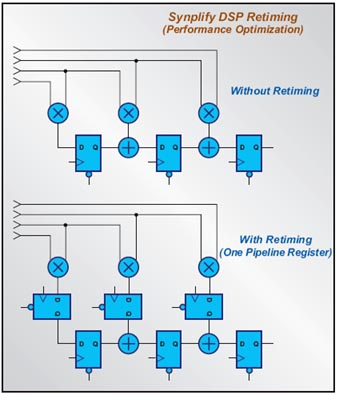

可以把折叠功能与另一优化功能-重定时功能结合起来使用。如果系统不满足目标频率要求,可以增加流水线级数,直到获得所需速率。这种做法对于使用高折叠系数的电路尤为重要,因为这类电路需要以相对较高的系统速度工作。

您还可以为折叠很少或没有折叠的电路使用重定时,除非已经达到FPGA的性能极限。可以通过增加流水线级数来减少两个寄存器之间组合逻辑门的数量(逻辑级数),这样可以提高系统时钟速度。

在生成RTL代码时,Synplify DSP工具将进行时序分析,它会考虑所需的采样频率、折叠系数和FPGA的目标架构。例如,与在较慢的低成本Spartan-3A DSP FPGA中实现的完全相同的电路相比,可以使用较少的流水线级数优化映射到快速Virtex-5 FPGA的电路。

可以用 FPGA提供的大量寄存器进行这种优化。寄存器可以大量使用,不像乘法器或LUT(查找表)那样很快会用光,这意味着可以使用寄存器轻而易举的显著提高系统时钟速度。

当然,增加流水线级数会增加系统延迟。例如,如果使用重定时系数8,计算结果就会迟8个系统时钟周期(不是采样频率周期)出现在FPGA的输出上。向系统中嵌入电路时必须考虑到这一点(图6)。

图6:可以使用重定时功能为电路定义允许的最大延迟。然后由Synplify DSP自动增加流水线级数,直到获得所需频率。

特别重要的是,务必确保上述优化不会影响Simulink中描述的原始MATLAB模型。通过验证可以对算法进行鉴定,并且对量化效应的影响予以表述。Synplify DSP软件模块集允许使用截断(去除无关位)、四舍五入(在下溢情况下)或饱和(在上溢情况下)进行从浮点到定点的转换。一旦仿真显示算法工作正常,即可生成RTL代码。优化VHDL或Verilog代码可能改变延迟,但不会改变电路的操作。

可以在Simulink中用Synplify DSP模块集和Simulink的滤波器设计与分析(FDA)工具实现该电路。FDA工具可帮助生成和验证各种FIR和IIR滤波器。该工具是Simulink信号处理工具箱的组成部分,Synplify DSP就是使用此工具箱实现滤波器结构。

Synplify DSP模块集或FDA工具提供的所有电路元件在PortIN和PortOUT描述之间都有定义,它们能够生成VHDL或Verilog代码。 Simulink模块集中的FFT和SCOPE元件对动态响应进行频谱分析和验证。这些模块专门用于功能验证,包括浮点到定点转换功能(量化)。这些模块都不用硬件实现。

算法实现的第一部分包括两个FIR滤波器:第一个滤波器有512个抽头,第二个滤波器有6?个抽头。因此,由过采样生成的RTL代码共含有576个乘法运算,这正是使用FPGA显得并不具有商业可行性的原因。这么大的FPGA会受到成本制约,因为需要用到有 6?0个DSP48模块的特大型Xilinx Virtex-5 XC5VSX95T器件。

未映射到专用硬件结构(DSP模块)的所有乘法运算都必须用通用逻辑资源(LUT或寄存器)构建。这样会导致资源要求上升而最高时钟速度下降。与通用逻辑单元相比,专用的DSP48模块作为乘法器会有效得多(图4)。

图4:用Simulink的滤波器设计与分析(FDA)工具实现滤波器。

设计优化

Synplify DSP的折叠选项可用来尽量减少所用乘法器的数量。在低采样频率下工作的电路尤其可从这一优化中受益。

其原理很简单。通常,每个乘法运算使用一个硬件乘法器,即使对于千赫级采样频率也是如此。然而,FPGA能以数百兆赫级的时钟速度工作。如果硬件乘法器在FPGA的系统频率下工作,就可以用时间多路复用过程按时序处理乘法运算。

假设电路的采样频率是3MHz,而FPGA最高可以在120MHz频率下运行。如果以系统频率运行乘法器,则每个硬件乘法器可以执行40次运算。此时所需硬件可以减少40倍。也就是说可以将上述采样率转换器(或使用低采样频率的任何其他电路)“折叠”到仅需要很少硬件乘法器的程度。所以,也可以在现有最小的低成本FPGA中实现这种转换器,从而真正取代DSP。

当然,还可能将计算量特别大的算法从DSP卸载到FPGA,从而减轻处理器的负荷。如果您的DSP应用已经超过性能极限,而且您已经为针对特定DSP架构的应用源代码作出大量投入,那么这种方法尤其有用(图5)。

图5:可以用折叠功能显著减少所需的FPGA资源。

因为Synplify DSP中的折叠功能还支持多速率系统,所以与只有一种采样频率的系统相比,您可以进一步减少所需乘法器的数量。过采样使用两个FIR滤波器完成。这两个滤波器以不同的采样频率运行。以较高采样频率运行的滤波器可以用您指定的折叠系数进行折叠。

以较低采样频率运行的滤波器用相对较高的系数折叠。获得此系数的方法是用两个滤波器的采样频率之差乘以折叠系数。例如,如果一个滤波器的采样频率是另一滤波器的8倍,则较快的滤波器用系数 8折叠,而较慢的滤波器用系数6?折叠。

这样甚至可能生成以通常不能折叠的很高采样率运行的空间优化电路。例如,如果系统以 200MHz采样率运行并使用折叠系数2,那么系统频率就可以提高到400MHz。

您还可以将折叠系数定义为1。以最高采样率运行的电路元件不折叠。但是,以较低采样频率运行的多速率系统的所有电路元件都可从折叠和空间优化实现中受益。您只需将系统作为整体为其定义折叠系数即可。然后,折叠会自动传播到所有采样频率。

可以把折叠功能与另一优化功能-重定时功能结合起来使用。如果系统不满足目标频率要求,可以增加流水线级数,直到获得所需速率。这种做法对于使用高折叠系数的电路尤为重要,因为这类电路需要以相对较高的系统速度工作。

您还可以为折叠很少或没有折叠的电路使用重定时,除非已经达到FPGA的性能极限。可以通过增加流水线级数来减少两个寄存器之间组合逻辑门的数量(逻辑级数),这样可以提高系统时钟速度。

在生成RTL代码时,Synplify DSP工具将进行时序分析,它会考虑所需的采样频率、折叠系数和FPGA的目标架构。例如,与在较慢的低成本Spartan-3A DSP FPGA中实现的完全相同的电路相比,可以使用较少的流水线级数优化映射到快速Virtex-5 FPGA的电路。

可以用 FPGA提供的大量寄存器进行这种优化。寄存器可以大量使用,不像乘法器或LUT(查找表)那样很快会用光,这意味着可以使用寄存器轻而易举的显著提高系统时钟速度。

当然,增加流水线级数会增加系统延迟。例如,如果使用重定时系数8,计算结果就会迟8个系统时钟周期(不是采样频率周期)出现在FPGA的输出上。向系统中嵌入电路时必须考虑到这一点(图6)。

图6:可以使用重定时功能为电路定义允许的最大延迟。然后由Synplify DSP自动增加流水线级数,直到获得所需频率。

特别重要的是,务必确保上述优化不会影响Simulink中描述的原始MATLAB模型。通过验证可以对算法进行鉴定,并且对量化效应的影响予以表述。Synplify DSP软件模块集允许使用截断(去除无关位)、四舍五入(在下溢情况下)或饱和(在上溢情况下)进行从浮点到定点的转换。一旦仿真显示算法工作正常,即可生成RTL代码。优化VHDL或Verilog代码可能改变延迟,但不会改变电路的操作。

FPGA DSP VHDL Verilog 仿真 滤波器 电路 Xilinx 解码器 赛灵思 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)