利用Nios II进行多媒体广告系统设计

时间:11-13

来源:互联网

点击:

引言

多媒体广告是当今企业与消费者交流、展示自我形象的一个平台,传统形式的广告业务制作成本高,周期长,内容模式固化僵硬,相对于市场变化有很大滞后性。电子屏的出现,不仅可以使企业更全面的展示产品,推广企业文化,而且可以满足不同读者的需求,改善城市环境,提升人民生活质量,更重要的是广告能够更及时、更准确、更全面的展示自己的新产品,第一时间与消费者进行沟通,赢得市场,获取利润,以及根据市场动态更及时更全面的做出市场决策。基于以上原因,我们采用Nios II软核设计了能及时发布户外广告、电子公告的多媒体广告系统。

1 多媒体广告系统所用技术简介

1.1 SOPC技术

SOPC是可编程片上系统(System On Programmablechip)的简称,是Altera公司提出的一种在可编程逻辑器件上灵活、高效实现SOC的解决方案。将处理器、存储器、I/O、LVDS、CDR等系统设计模块集成到一枚FPGA或者CPLD上,构成一种可编程的片上系统。SOPC是一种特殊的嵌入式系统:首先它是片上系统SOC;其次它是可编程系统,具有灵活的设计方式,可裁剪、扩充、升级,并且具备软硬件在系统可编程的功能。FPGA则是SOPC的高效设计平台。本系统是在Altera公司的DE1上实现,FPGA采用的是Cyclone II EP2C20F484C7。伴随着Nios的发展,Altera的SOPC概念逐渐为人们所接受,进而又推出了第二代处理器软核Nios II,提高了处理能力、减少了资源占用,并在价格上拥有相当大的优势,进一步推动了SOPC的发展。系统模块在SOPC中可方便集成为一个系统。系统如图1所示:

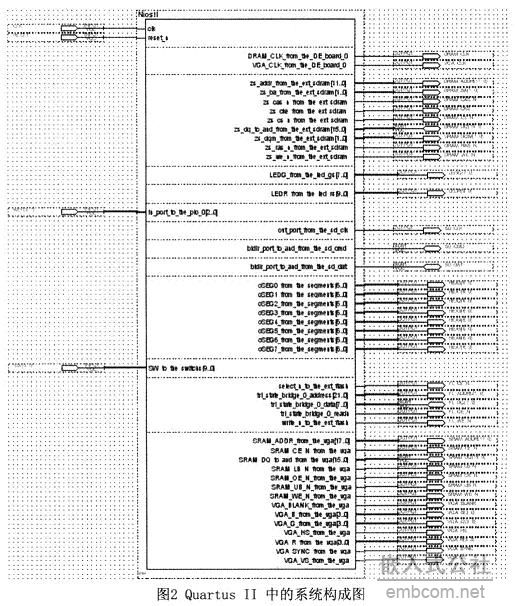

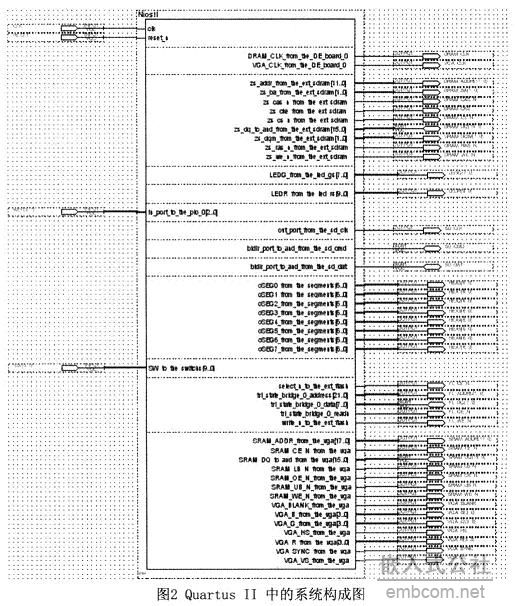

在Quartus II下搭建的系统如图2所示:

设计方法与实现步骤:

整个设计采用自顶向下的设计方法,在设计之初我们先描绘出整个设计所涉及的各个部件和功能模块,然后在SOPC Builder中搭建各硬件模块,各模块通过Avalon总线有序的连接在一起。SOPC Builder的图形可视化设计,大大的方便了系统硬件的设计,尤其是Avalon总线的引入可以让设计人员从繁琐的细节问题和代码编写上解放出来,将精力集中与系统框架的整体设计和用户程序的编写之上。

1.2 Nios II软核处理器

Nios II是一种拥有超过200DMIPS性能的32位RISC处理器IP核,其外设与处理器本身都是使用HDL编写的,可以在Altera几乎所有的FPGA中实现。由于处理器是软核形式,可以根据应用的需要自由定制,满足成本和功能的要求,因此具有很大的灵活性。Nios II系列嵌入式处理器建立在第一代16位Nios处理器的基础上,使用32位的指令集结构(ISA),定位于广泛的嵌入式应用。Nios II处理器系列包含3种内核:快速型(Nios II/f)、经济型(NiosII/e)和标准型(Nios II/s)内核。每一种内核都针对资源和性能作了特定的优化。由于多媒体信息的操作对系统处理器运算速度有着较高的要求,所以采用了快速型的内核。快速型内核的处理速度最快可达到200DMIPS,工作频率是135MHz,支持6级流水线,外部寻址空间为2GB。保证了系统的实时性和稳定性。使用Altera的Quartus II软件、SOPC Bulilder工具以及Nios II集成开发环境(IDE)完成了基于Nios II的嵌入式系统开发。

2 系统的构成

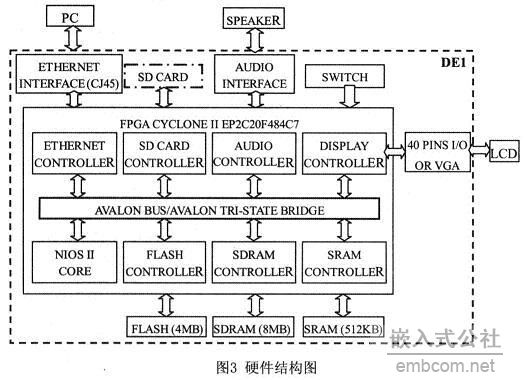

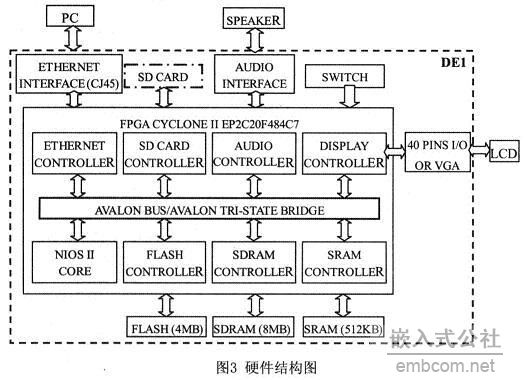

多媒体广告系统主要由上下位机通信模块、嵌入FPGA的Nios II处理器、视频音频输出模块、下位机存储模块等组成。系统的硬件结构图如图3所示。

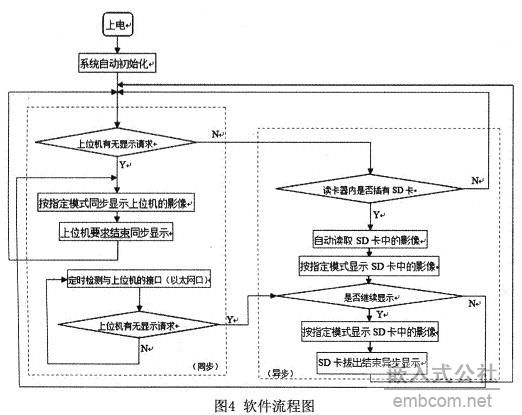

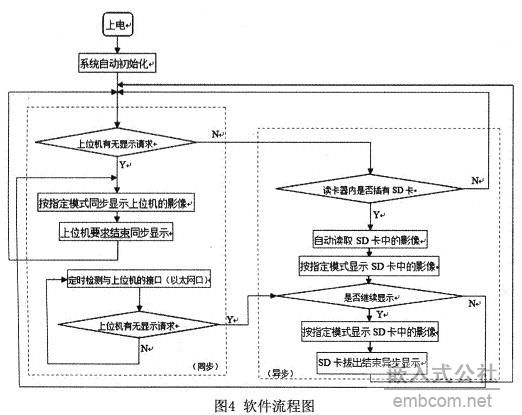

由于多媒体广告的投放发布有实时和非实时之分,所以系统的工作模式也分为同步与异步两种。系统的软件流程图如图4所示。

2.1 通信模块

模块集成了LAN91C111 Ethernet MAC,同时使用Nios II IDE建立了基于uC/OS II操作系统的TCP/IPSocket server工程,该应用工程能够初始化IwIP(Lightweigh IP)stack,运行简单的TCP Server。PC机通过Ethernet与下位机通信。另外在上位机上编写了一个与下位机通信的软件,该软件主要是用于多媒体广告的同步投放,以及将要用于异步投放的多媒体广告信息下载到下位机的存储器中。

2.2 IP核

IP核是知识产权核(Intellectual Propety Kernel)的简称,主要将一些在数字电路中常用的但比较复杂的功能块设计成参数可修改的模块,让其他用户可以直接调用这些模块。本设计中主要用到了存储控制器IP CORE和多媒体信息输出控制器IP CORE。

2.3 SD卡的读写驱动模块

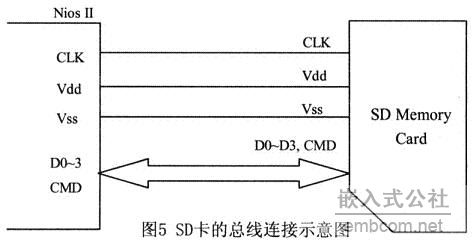

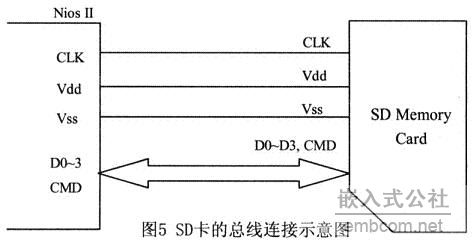

多媒体广告文件的数据量较大,因此采用SD卡作为多媒体文件的存储器。通过Nios II的I/O口与SD卡相连,采用SD模式对其进行读写的操作,实现对数据的4线高速传输。如图5所示。

2.4 异步模式下显示方式控制模块

为了满足不同风格多媒体广告的在异步模式下投放需要,将DE1平台上的10个开关通过I/O口与Nios II连接,拨动不同的开关来设定广告的显示方式,从而达到更好的显示效果,目前已实现的显示方式有:组合分屏显示、多幅图像分屏显示、单幅图像循环显示、单幅分屏显示、单幅分屏显示加旋转、单幅重复显示等。

3 结语

本文设计的多媒体广告系统基于Nios II处理器,易于升级、运行速度快、稳定、功耗低,能很好的满足户外多媒体广告的投放需要。

多媒体广告是当今企业与消费者交流、展示自我形象的一个平台,传统形式的广告业务制作成本高,周期长,内容模式固化僵硬,相对于市场变化有很大滞后性。电子屏的出现,不仅可以使企业更全面的展示产品,推广企业文化,而且可以满足不同读者的需求,改善城市环境,提升人民生活质量,更重要的是广告能够更及时、更准确、更全面的展示自己的新产品,第一时间与消费者进行沟通,赢得市场,获取利润,以及根据市场动态更及时更全面的做出市场决策。基于以上原因,我们采用Nios II软核设计了能及时发布户外广告、电子公告的多媒体广告系统。

1 多媒体广告系统所用技术简介

1.1 SOPC技术

SOPC是可编程片上系统(System On Programmablechip)的简称,是Altera公司提出的一种在可编程逻辑器件上灵活、高效实现SOC的解决方案。将处理器、存储器、I/O、LVDS、CDR等系统设计模块集成到一枚FPGA或者CPLD上,构成一种可编程的片上系统。SOPC是一种特殊的嵌入式系统:首先它是片上系统SOC;其次它是可编程系统,具有灵活的设计方式,可裁剪、扩充、升级,并且具备软硬件在系统可编程的功能。FPGA则是SOPC的高效设计平台。本系统是在Altera公司的DE1上实现,FPGA采用的是Cyclone II EP2C20F484C7。伴随着Nios的发展,Altera的SOPC概念逐渐为人们所接受,进而又推出了第二代处理器软核Nios II,提高了处理能力、减少了资源占用,并在价格上拥有相当大的优势,进一步推动了SOPC的发展。系统模块在SOPC中可方便集成为一个系统。系统如图1所示:

在Quartus II下搭建的系统如图2所示:

设计方法与实现步骤:

整个设计采用自顶向下的设计方法,在设计之初我们先描绘出整个设计所涉及的各个部件和功能模块,然后在SOPC Builder中搭建各硬件模块,各模块通过Avalon总线有序的连接在一起。SOPC Builder的图形可视化设计,大大的方便了系统硬件的设计,尤其是Avalon总线的引入可以让设计人员从繁琐的细节问题和代码编写上解放出来,将精力集中与系统框架的整体设计和用户程序的编写之上。

1.2 Nios II软核处理器

Nios II是一种拥有超过200DMIPS性能的32位RISC处理器IP核,其外设与处理器本身都是使用HDL编写的,可以在Altera几乎所有的FPGA中实现。由于处理器是软核形式,可以根据应用的需要自由定制,满足成本和功能的要求,因此具有很大的灵活性。Nios II系列嵌入式处理器建立在第一代16位Nios处理器的基础上,使用32位的指令集结构(ISA),定位于广泛的嵌入式应用。Nios II处理器系列包含3种内核:快速型(Nios II/f)、经济型(NiosII/e)和标准型(Nios II/s)内核。每一种内核都针对资源和性能作了特定的优化。由于多媒体信息的操作对系统处理器运算速度有着较高的要求,所以采用了快速型的内核。快速型内核的处理速度最快可达到200DMIPS,工作频率是135MHz,支持6级流水线,外部寻址空间为2GB。保证了系统的实时性和稳定性。使用Altera的Quartus II软件、SOPC Bulilder工具以及Nios II集成开发环境(IDE)完成了基于Nios II的嵌入式系统开发。

2 系统的构成

多媒体广告系统主要由上下位机通信模块、嵌入FPGA的Nios II处理器、视频音频输出模块、下位机存储模块等组成。系统的硬件结构图如图3所示。

由于多媒体广告的投放发布有实时和非实时之分,所以系统的工作模式也分为同步与异步两种。系统的软件流程图如图4所示。

2.1 通信模块

模块集成了LAN91C111 Ethernet MAC,同时使用Nios II IDE建立了基于uC/OS II操作系统的TCP/IPSocket server工程,该应用工程能够初始化IwIP(Lightweigh IP)stack,运行简单的TCP Server。PC机通过Ethernet与下位机通信。另外在上位机上编写了一个与下位机通信的软件,该软件主要是用于多媒体广告的同步投放,以及将要用于异步投放的多媒体广告信息下载到下位机的存储器中。

2.2 IP核

IP核是知识产权核(Intellectual Propety Kernel)的简称,主要将一些在数字电路中常用的但比较复杂的功能块设计成参数可修改的模块,让其他用户可以直接调用这些模块。本设计中主要用到了存储控制器IP CORE和多媒体信息输出控制器IP CORE。

2.3 SD卡的读写驱动模块

多媒体广告文件的数据量较大,因此采用SD卡作为多媒体文件的存储器。通过Nios II的I/O口与SD卡相连,采用SD模式对其进行读写的操作,实现对数据的4线高速传输。如图5所示。

2.4 异步模式下显示方式控制模块

为了满足不同风格多媒体广告的在异步模式下投放需要,将DE1平台上的10个开关通过I/O口与Nios II连接,拨动不同的开关来设定广告的显示方式,从而达到更好的显示效果,目前已实现的显示方式有:组合分屏显示、多幅图像分屏显示、单幅图像循环显示、单幅分屏显示、单幅分屏显示加旋转、单幅重复显示等。

3 结语

本文设计的多媒体广告系统基于Nios II处理器,易于升级、运行速度快、稳定、功耗低,能很好的满足户外多媒体广告的投放需要。

电子 Altera FPGA CPLD 嵌入式 Quartus 总线 MIPS 电路 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)