数字下变频的FPGA实现

时间:05-12

来源:互联网

点击:

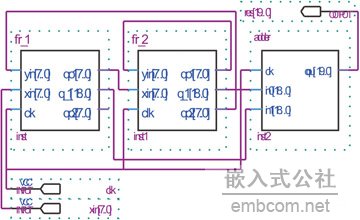

图3 16阶FIR滤波器的级联结构图

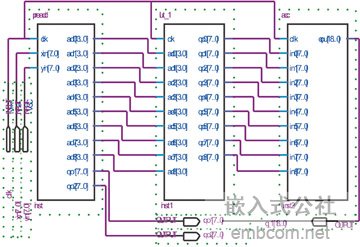

图4 FIR滤波器子模块结构图

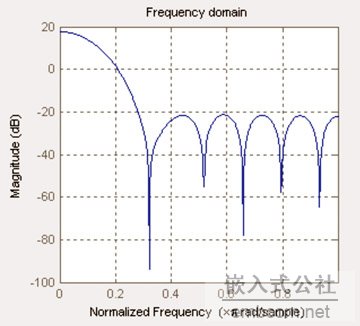

图5 16阶FIR滤波器响应曲线图

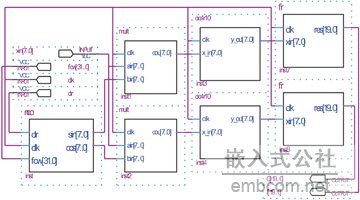

图6 DDC实现的结构图

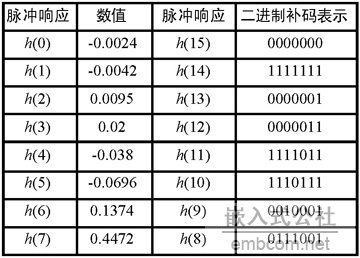

这种结构的滤波器结构简单、易于实现,很容易扩展成高阶滤波器。首先通过MATLAB中的FirDesignTool工具得到滤波器的系数图表(表1)。利用线性FIR滤波器抽头系数的对称性,通过加法器将对称的系数进行预相加,从而降低硬件规模。根据分布式算法原理,通过将抽头系数的所有可能组合固化在ROM中,利用查找表来代替乘法器。利用预相加模块产生的地址来查找ROM表,并将相应的数值进行移位相加,从而得出正确的结果。

表1 16阶FIR滤波器系数

DDC系统的实现

利用上述的各个模块,可得到DDC系统的实现结构图如图6所示。

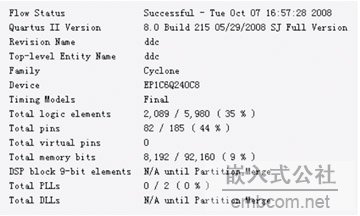

整个系统在Cyclone系列芯片EP1C6Q240C8上实现,其FPGA综合结果图7所示。

图7 DDC系统的Quartus综合结果

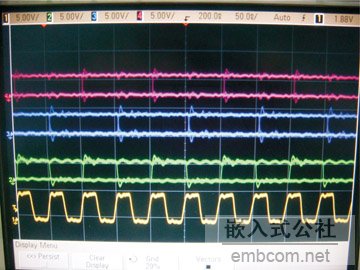

图8 系统时序测试结果

时序测试图(图8)中,黄色为系统时钟波形,绿色为NCO产生的正弦波时序波形,蓝色为抽取滤波器输出的时序波形,粉红色为FIR滤波器输出时序波形。从示波器显示的时序图可以看出抽取滤波器输出波形的延时最大,大约为14ns左右,这和软件仿真的结果比较吻合,仿真中抽取滤波器输出的延时为16.47ns。故抽取滤波器是制约系统时钟速率提高的关键因素。

结语

本文介绍了一种应用于数字化中频频谱分析仪的数字下变频电路,整个电路基于FPGA实现,结构简单,易于编程实现。

频谱分析仪 DSP FPGA 振荡器 滤波器 低通滤波器 VHDL Quartus 示波器 仿真 电路 相关文章:

- 基于AVR和FPGA高精度数字式移相发生器的设计(11-07)

- 基于FPGA的简易频谱分析仪的设计方案(11-08)

- 全面掌控频域(07-01)

- 基于FPGA的简易频谱分析仪(11-12)

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)