基于ARM的嵌入式系统中从串配置FPGA的实现

时间:06-09

来源:互联网

点击:

4 软件设计

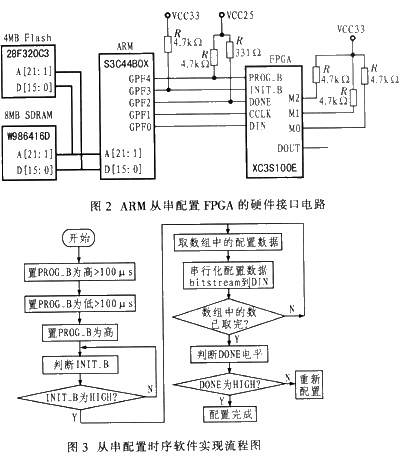

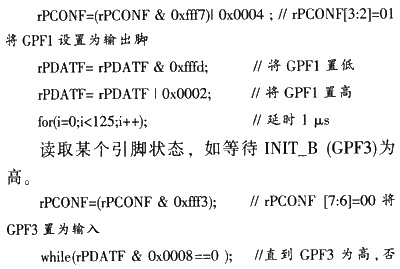

软件设计流程如图3所示。配置软件的编程要确保ARM完全按照配置信号的时序工作,关键问题

是采用S3C44BOX的通用I/O口GPF0、GPF1、GPF2、GPF3、GPF4模拟DIN、CCLK、DONE、INIT_B、PROG_B的时序。

在S3C44BOX中,大多数引脚都是多功能引脚,可以通过端口配置寄存器选择相应的引脚功能。

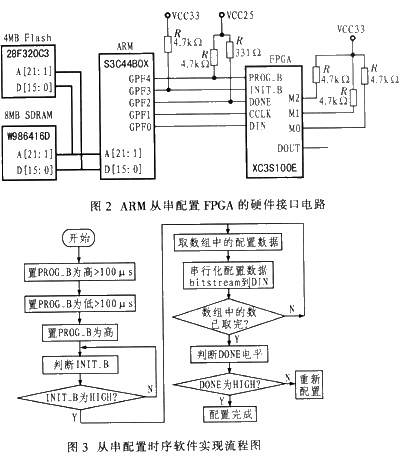

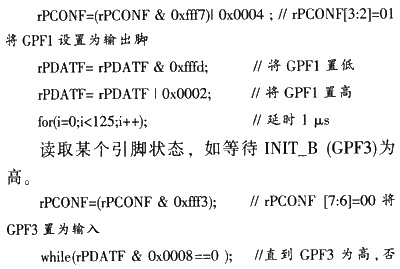

以端口F为例,控制寄存器rPCONF用作设定引脚的输入、输出或特殊功能;数据寄存器rPDATF[0:8]对应于GPF0~GPF8引脚上的数据。读写寄存器rPDATF的各个位对应于引脚的读或写。例如,CCLK上升沿时序是向GPF1先写0,再写1得到,延时程序则由for循环实现。

则一直循环等待

CCLK在每个上升沿把1 bit的数据置入DIN中,先将GPF1置低,在GPF0准备好1 bit数据,再将GPF1置高即可,以此循环将config_data_array[]中的每个字节按先低位再高位的次序写入FPGA。

Xilinx的FPGA配置文件大小相同,与FPGA内部逻辑设计的复杂度无关。以Spartan_3E系列的10万门FPGA XC3S100E为例,它的配置文件固定为581 344 bit,若CCLK的时钟周期置为2μs,配置时间约为1.2 s。

5 实验结果验证

验证环境:硬件采用自行开发的实验板和武汉创维特公司的:JTAG硬件仿真器;软件则使用Xilinx公司的开发工具ISE8.1和武汉创维特公司的集成开发环境ADT 1000(支持ARM7,ARM9)。

利用VerilogHDL编写程序led.v在七段数码管上循环显示0~F,采用:ISE8.1编译、综合、映射、布局布线。生成用于编程专用PROM的led.bin文件。用一个简单的C程序将.bin文件转换成ASCⅡ码文件,再将ASCⅡ码文件复制到配置数据数组config_data_array[]中,然后在ADT环境下编译配置程序、配置数据和系统程序,将生成的.bin文件通过JTAG口烧写到Flash中。重新上电后,FPGA配置正常,实验结果与预设相一致。

6 结束语

基于ARM的FPGA从串配置方案结构简单、接线容易、软件编程简单,非常适用于嵌入式系统设计。虽然该控制电路是为Xilinx公司Spartan-3E系列的FPGA设计的,但稍加修改也可用于其他系列FPGA器件,故具有一定的通用性。另外,由于FPGA具有可重复配置的灵活性,在嵌入式系统中可通过串口、网口远程烧写Flash,重构系统功能,这种在线重构技术为设备的智能化在线维护、功能重组和在线升级等提供了可能,而且灵活性很强。本文提出的方案对数字系统设计具有借鉴意义,有着广阔的应用前景。

软件设计流程如图3所示。配置软件的编程要确保ARM完全按照配置信号的时序工作,关键问题

是采用S3C44BOX的通用I/O口GPF0、GPF1、GPF2、GPF3、GPF4模拟DIN、CCLK、DONE、INIT_B、PROG_B的时序。

在S3C44BOX中,大多数引脚都是多功能引脚,可以通过端口配置寄存器选择相应的引脚功能。

以端口F为例,控制寄存器rPCONF用作设定引脚的输入、输出或特殊功能;数据寄存器rPDATF[0:8]对应于GPF0~GPF8引脚上的数据。读写寄存器rPDATF的各个位对应于引脚的读或写。例如,CCLK上升沿时序是向GPF1先写0,再写1得到,延时程序则由for循环实现。

则一直循环等待

CCLK在每个上升沿把1 bit的数据置入DIN中,先将GPF1置低,在GPF0准备好1 bit数据,再将GPF1置高即可,以此循环将config_data_array[]中的每个字节按先低位再高位的次序写入FPGA。

Xilinx的FPGA配置文件大小相同,与FPGA内部逻辑设计的复杂度无关。以Spartan_3E系列的10万门FPGA XC3S100E为例,它的配置文件固定为581 344 bit,若CCLK的时钟周期置为2μs,配置时间约为1.2 s。

5 实验结果验证

验证环境:硬件采用自行开发的实验板和武汉创维特公司的:JTAG硬件仿真器;软件则使用Xilinx公司的开发工具ISE8.1和武汉创维特公司的集成开发环境ADT 1000(支持ARM7,ARM9)。

利用VerilogHDL编写程序led.v在七段数码管上循环显示0~F,采用:ISE8.1编译、综合、映射、布局布线。生成用于编程专用PROM的led.bin文件。用一个简单的C程序将.bin文件转换成ASCⅡ码文件,再将ASCⅡ码文件复制到配置数据数组config_data_array[]中,然后在ADT环境下编译配置程序、配置数据和系统程序,将生成的.bin文件通过JTAG口烧写到Flash中。重新上电后,FPGA配置正常,实验结果与预设相一致。

6 结束语

基于ARM的FPGA从串配置方案结构简单、接线容易、软件编程简单,非常适用于嵌入式系统设计。虽然该控制电路是为Xilinx公司Spartan-3E系列的FPGA设计的,但稍加修改也可用于其他系列FPGA器件,故具有一定的通用性。另外,由于FPGA具有可重复配置的灵活性,在嵌入式系统中可通过串口、网口远程烧写Flash,重构系统功能,这种在线重构技术为设备的智能化在线维护、功能重组和在线升级等提供了可能,而且灵活性很强。本文提出的方案对数字系统设计具有借鉴意义,有着广阔的应用前景。

ARM 电子 FPGA Xilinx 嵌入式 虚拟仪器 电压 电阻 仿真 Verilog 电路 相关文章:

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 基于ARM9和CPLD的输入输出系统设计(04-09)

- FPGA中的处理器IP概述(04-14)

- FPGA与DS18B20型温度传感器通信的实现(07-09)

- 基于ARM的FPGA加载配置实现(07-18)