高速FPGA系统的信号完整性测试和分析

时间:01-23

来源:互联网

点击:

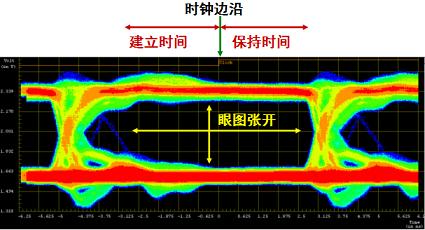

图6 TLA逻辑分析仪上显示多通道眼图测试结果

6. 小结

对于FPGA中的高速串行和并行IO信号,需要根据被测信号特点和速度来选择合适的测试和分析工具。当测试信号完整性,希望得到最精确的上升时间,下降时间,信号过冲和震铃等参数,带宽是首要选择。某种意义上带宽越高,测试精度越高。对于实时示波器而言,高速采集内存是眼图和抖动等信号完整性测试的关键。对于采样示波器,通过CSA/TDS8200配合80SJNB抖动和噪声分析软件,不仅可以精确的测量高速串行信号的抖动和噪声,并且能够根据测量结果进行精确的抖动、噪声中每一个分量的分离,和系统的BER相关,最终为信号完整性验证人员提供有价值的信息。当测试高速时钟或数据抖动时,泰克两种示波器都配备业内推荐的抖动测试和分析软件,帮助设计人员得到抖动结果,分析抖动产生的原因,最终得到高可靠性的系统。

FPGA 总线 电路 示波器 泰克 电压 ADC 半导体 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)