基于MSP430的石油井下压力测试系统的设计

时间:01-23

来源:互联网

点击:

1 引言

压力数据在油田开采过程中是一项极重要的资料。而这其中的射孔工艺是关键环节,其对高质量打开油气层,提高油气井产能都有重要影响。射孔是打开油气层让地层流体流入井内的主要完井工序。测取射孔瞬间动态压力参数具有重要意义;确定每次射孔的施工效果;结合其他测试参数评价地质效果:研究射孔工艺机理,为我国射孔理论水平的发展创造有利条件。该参数的测取也是研究油气层特征,掌握油气层动态。检查地面采油工艺流程的重要手段。为此,必须借助于各种精密的压力测量仪表。以获得精确的压力数据。

2 测试系统设计

2.1 存储测试原理简介

存储测试系统是用以完成存储测试的物理系统,可工作在高温、高压、强冲击振动、高过载等恶劣环境下,自动完成被测信息的实时采集与存储记忆。它将传感器、适配电路、数字化存储记录电路、通讯接口、控制指示单元和电源集成为一体,构成一个小型化的、可安装在被测体内(相对)独立丁作的测试系统。由于存储测试系统具有体积小、功耗低、可重复使用、抗干扰性好及能适应特殊环境等特点,所以对于工程测试,特别是在野外恶劣的环境下,存储测试系统提供了一个很好的解决方案。

这里设计的仪器必须能够在高温、高压、高冲击的油井中安全、可靠的取得射孔压裂数据,且能保持数据长时间不丢失,可顺利回收被测信息。因此该系统除需能耐高温、高压、高冲击振动的电路外,还必须对其保护,防止仪器损坏。

2.2 系统工作原理

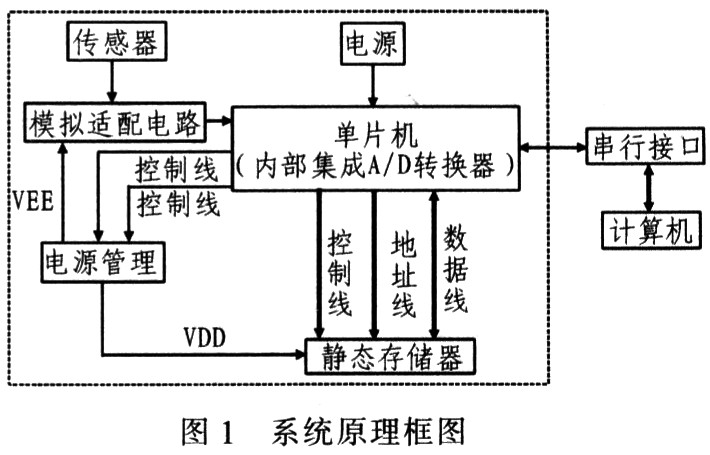

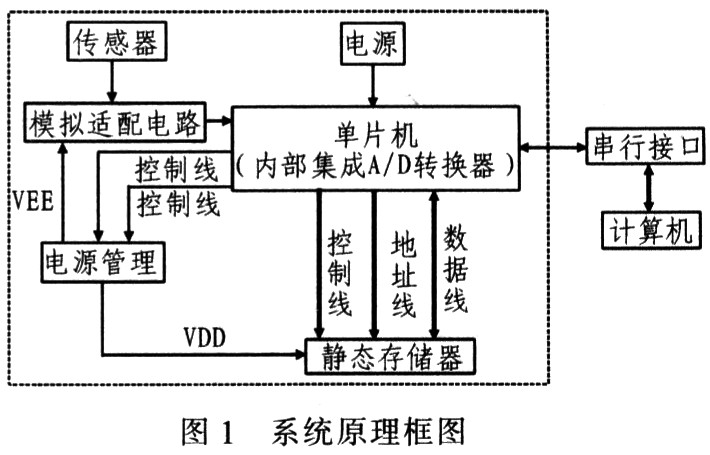

系统原理框图如图1所示。

石油井下射孔压力测试系统选用编程自适应分段均匀采样策略,即通过事先编程确定记录过程分为若干个均匀采样阶段,每一阶段的开始时间、采样频率、存储点数是根据被测信号的变化自适应调整的。此系统在单片机程序的控制下,上电延时50s后,在触发信号到来之前,以1Hz的采样频率进行低频采样A/D转换,并将MD转换输出的数据存人存储器。触发信号到来后,开始以100kHz的采样频率采样,连续采样满128K字数据,再以500Hz采样,至采满256K字,数据停止采样。当电路回收后,可通过RS232接口将存储器中的数据读至计算机.以便后续处理。

2.3 MSP430单片机低功耗的设计

MSP430系列单片机具有独特的时钟系统设计,包括两个不同的时钟系统:基本时钟系统和锁频环(FLL和FLL+)时钟系统或数字振荡器(DCO)时钟系统。由时钟系统产生CPU和各功能模块所需时钟,这些时钟可在指令的控制下打开或关闭,从而控制总体功耗。由于系统运行时所使用的功能模块不同,即采用不同的工作模式,器件的功耗有明显区别。系统具有1种活动模式(AM)和5种低功耗模式(LPM0~LPM4)。MSP430系列单片机各个模块运行完全独立,定时器、输入/输出端口、A/D转换、看门狗等都可在主CPU休眠的状态下独立运行。当需要主CPU工作时,任何一个模块都可以通过中断唤醒CPU,从而使系统以最低功耗运行。这是MSP430系列单片机最突出的优点。

为充分利用CPU的低功耗性能,使其工作于突发状态。通常情况下,根据需要使用软件将CPU设定到某一种低功耗工作模式下,在需要时使用中断将CPU从休眠状态中唤醒,完成工作后又可进入相应休眠状态。图2为MSP430F1611单片机的基本配置电路。

3 状态设计及系统状态分析

3.1 状态设计理论

状态设计是指根据被测对象的运动规律确定存储测试系统状态组织结构的过程。它是实现功能设计的关键环节,是硬件设计的依据,也是建立基型存储测试系统的有效手段。状态设计可以使设计思想始终清晰地贯穿于设计和调试,不同程度地简化原本复杂的设计过程。

3.2 系统的状态分析

根据状态分析,存储测试系统完成一次有效的数据测试,大致需经6个过程:等待状态A0,低速采存状态A1,高速采存状态A2,低速采存状态A3,信息保持状态A4,数据读出状态A5。MSP430F1611通过控制ONA、ONB分别产生VDD=3.6V、VEE=3.6V,OE、WE、CE分别为存储器的读、写、片选控制信号。ONA信号为低电平时输出VDD,为高电平时关闭。ONB为低电平时输出VEE,为高电平时关闭。图3为系统状态转换图,详细分析系统各工作阶段的电源开闭情况及低功耗模式。

等待状态A0对系统进行初始化,复位操作。其中,在I/O初始化中,设置上电外部中断,当ONA、ONB为OE、WE、CE为低,电源VDD、VEE关闭,初始化通用寄存器,将内部DCO晶振8分频,初始化定时器A,通过TA中断延时50s.等待电源稳定后进入低功耗1。

低速采存状态A1中,延时50s后,使ONA、ONB、CE为低,OE、WE为高,电源VDD、VEE打开,存储器片选端有效,初始化时钟,使子系统时钟设置为外部高频时钟源.初始化A/D转换器并设置单通道单次转换模式,初始化定时器B,由TB中断实现采存,初始化中TB每隔0.01ms中断一次,在采存过程中A/D转换器一直处于100kHz的高速采样状态。并将数据送入FIFO。频率变换则通过存储器推地址来实现,此状态是采样射孔前井下静压,因此采用1Hz进行低速采存。

高速采存状态A2中,将128K作为是否变频的标志,ONA、ONB、CE为低,OE、WE为高,电源VDD、VEE打开,存储器读、写端有效,由数字内触发方式实现触发变频。当触发信号来临,改变存储器推地址,实现100kHz高速采存。低速采存状态A3中,ONA、ONB、CE为低,OE、WE为高电源VDD、VEE打开,存储器读、写端有效,改变存储器推地址,实现500Hz低速采存,将256K作为是否采满的标志。

信息保持状态A4中,定时器A、定时器B禁止中断,ONA为低,ONB、OE、WE、CE为高,打开VDD=3.6V,存储器处于有效状态,于是数据保存在存储器内,关闭A/D转换器,清零地址位,进入低功耗4模式,等待读数中断。数据读出状态A5中,通过读数中断初始化串口读数,设置时钟为外部8MHz高频晶振,通过串口向计算机传输采存到的数据,读数完毕进入低功耗4模式。

压力数据在油田开采过程中是一项极重要的资料。而这其中的射孔工艺是关键环节,其对高质量打开油气层,提高油气井产能都有重要影响。射孔是打开油气层让地层流体流入井内的主要完井工序。测取射孔瞬间动态压力参数具有重要意义;确定每次射孔的施工效果;结合其他测试参数评价地质效果:研究射孔工艺机理,为我国射孔理论水平的发展创造有利条件。该参数的测取也是研究油气层特征,掌握油气层动态。检查地面采油工艺流程的重要手段。为此,必须借助于各种精密的压力测量仪表。以获得精确的压力数据。

2 测试系统设计

2.1 存储测试原理简介

存储测试系统是用以完成存储测试的物理系统,可工作在高温、高压、强冲击振动、高过载等恶劣环境下,自动完成被测信息的实时采集与存储记忆。它将传感器、适配电路、数字化存储记录电路、通讯接口、控制指示单元和电源集成为一体,构成一个小型化的、可安装在被测体内(相对)独立丁作的测试系统。由于存储测试系统具有体积小、功耗低、可重复使用、抗干扰性好及能适应特殊环境等特点,所以对于工程测试,特别是在野外恶劣的环境下,存储测试系统提供了一个很好的解决方案。

这里设计的仪器必须能够在高温、高压、高冲击的油井中安全、可靠的取得射孔压裂数据,且能保持数据长时间不丢失,可顺利回收被测信息。因此该系统除需能耐高温、高压、高冲击振动的电路外,还必须对其保护,防止仪器损坏。

2.2 系统工作原理

系统原理框图如图1所示。

石油井下射孔压力测试系统选用编程自适应分段均匀采样策略,即通过事先编程确定记录过程分为若干个均匀采样阶段,每一阶段的开始时间、采样频率、存储点数是根据被测信号的变化自适应调整的。此系统在单片机程序的控制下,上电延时50s后,在触发信号到来之前,以1Hz的采样频率进行低频采样A/D转换,并将MD转换输出的数据存人存储器。触发信号到来后,开始以100kHz的采样频率采样,连续采样满128K字数据,再以500Hz采样,至采满256K字,数据停止采样。当电路回收后,可通过RS232接口将存储器中的数据读至计算机.以便后续处理。

2.3 MSP430单片机低功耗的设计

MSP430系列单片机具有独特的时钟系统设计,包括两个不同的时钟系统:基本时钟系统和锁频环(FLL和FLL+)时钟系统或数字振荡器(DCO)时钟系统。由时钟系统产生CPU和各功能模块所需时钟,这些时钟可在指令的控制下打开或关闭,从而控制总体功耗。由于系统运行时所使用的功能模块不同,即采用不同的工作模式,器件的功耗有明显区别。系统具有1种活动模式(AM)和5种低功耗模式(LPM0~LPM4)。MSP430系列单片机各个模块运行完全独立,定时器、输入/输出端口、A/D转换、看门狗等都可在主CPU休眠的状态下独立运行。当需要主CPU工作时,任何一个模块都可以通过中断唤醒CPU,从而使系统以最低功耗运行。这是MSP430系列单片机最突出的优点。

为充分利用CPU的低功耗性能,使其工作于突发状态。通常情况下,根据需要使用软件将CPU设定到某一种低功耗工作模式下,在需要时使用中断将CPU从休眠状态中唤醒,完成工作后又可进入相应休眠状态。图2为MSP430F1611单片机的基本配置电路。

3 状态设计及系统状态分析

3.1 状态设计理论

状态设计是指根据被测对象的运动规律确定存储测试系统状态组织结构的过程。它是实现功能设计的关键环节,是硬件设计的依据,也是建立基型存储测试系统的有效手段。状态设计可以使设计思想始终清晰地贯穿于设计和调试,不同程度地简化原本复杂的设计过程。

3.2 系统的状态分析

根据状态分析,存储测试系统完成一次有效的数据测试,大致需经6个过程:等待状态A0,低速采存状态A1,高速采存状态A2,低速采存状态A3,信息保持状态A4,数据读出状态A5。MSP430F1611通过控制ONA、ONB分别产生VDD=3.6V、VEE=3.6V,OE、WE、CE分别为存储器的读、写、片选控制信号。ONA信号为低电平时输出VDD,为高电平时关闭。ONB为低电平时输出VEE,为高电平时关闭。图3为系统状态转换图,详细分析系统各工作阶段的电源开闭情况及低功耗模式。

等待状态A0对系统进行初始化,复位操作。其中,在I/O初始化中,设置上电外部中断,当ONA、ONB为OE、WE、CE为低,电源VDD、VEE关闭,初始化通用寄存器,将内部DCO晶振8分频,初始化定时器A,通过TA中断延时50s.等待电源稳定后进入低功耗1。

低速采存状态A1中,延时50s后,使ONA、ONB、CE为低,OE、WE为高,电源VDD、VEE打开,存储器片选端有效,初始化时钟,使子系统时钟设置为外部高频时钟源.初始化A/D转换器并设置单通道单次转换模式,初始化定时器B,由TB中断实现采存,初始化中TB每隔0.01ms中断一次,在采存过程中A/D转换器一直处于100kHz的高速采样状态。并将数据送入FIFO。频率变换则通过存储器推地址来实现,此状态是采样射孔前井下静压,因此采用1Hz进行低速采存。

高速采存状态A2中,将128K作为是否变频的标志,ONA、ONB、CE为低,OE、WE为高,电源VDD、VEE打开,存储器读、写端有效,由数字内触发方式实现触发变频。当触发信号来临,改变存储器推地址,实现100kHz高速采存。低速采存状态A3中,ONA、ONB、CE为低,OE、WE为高电源VDD、VEE打开,存储器读、写端有效,改变存储器推地址,实现500Hz低速采存,将256K作为是否采满的标志。

信息保持状态A4中,定时器A、定时器B禁止中断,ONA为低,ONB、OE、WE、CE为高,打开VDD=3.6V,存储器处于有效状态,于是数据保存在存储器内,关闭A/D转换器,清零地址位,进入低功耗4模式,等待读数中断。数据读出状态A5中,通过读数中断初始化串口读数,设置时钟为外部8MHz高频晶振,通过串口向计算机传输采存到的数据,读数完毕进入低功耗4模式。

传感器 电路 单片机 MSP430 振荡器 看门狗 信号发生器 相关文章:

- 传感器技术中的阻抗测量方法(03-23)

- 电桥测量基础(06-10)

- 适用于微型仪器的精密电容传感器接口(09-06)

- 基于PIR的移动检测系统的实现(11-03)

- 基于霍尔传感器的直流电机转速测量系统设计(11-14)

- NPXI智能传感器的TPMS系统设计(11-29)