一种数字控制的三相移相触发电路的设计

时间:10-26

来源:互联网

点击:

2.5 电路布局

移相触发集成电路采用1.2μm N阱双层多晶单层金属CMOS集成电路设计规则设计电路布局。采用全定制的布局设计方法。其特点是针对每个晶体管优化电路参数和布局以获得最佳性能以及最小面积。布局设计需解决的关键问题是减少衬底耦合噪声的影响,可通过以下途径解决:

(1)阱隔离环低掺杂的衬底中,物理隔离通过增加注入孔和感应孔间的距离来增加两者间的电阻,增强隔离效果。

(2)用P+扩散层形成隔离 P+扩散层通过吸收数字器件注入衬底的噪声电流达到隔离效果,隔离环用于包围数字电路或者是模拟电路。从另一个角度看,引入了P+隔离环后,减少环内的那部分衬底区域到地的电阻,也相应减小该区域受到的耦合噪声干扰。

(3)数字电路地与衬底分离将数字电路的N管的源极通过Metal接地,而不与衬底相连。衬底为模拟地,因此通过这种措施将模拟电路和数字电路地分开.模拟和数字电路通过地线耦合抑制噪声。

2.6 仿真结果

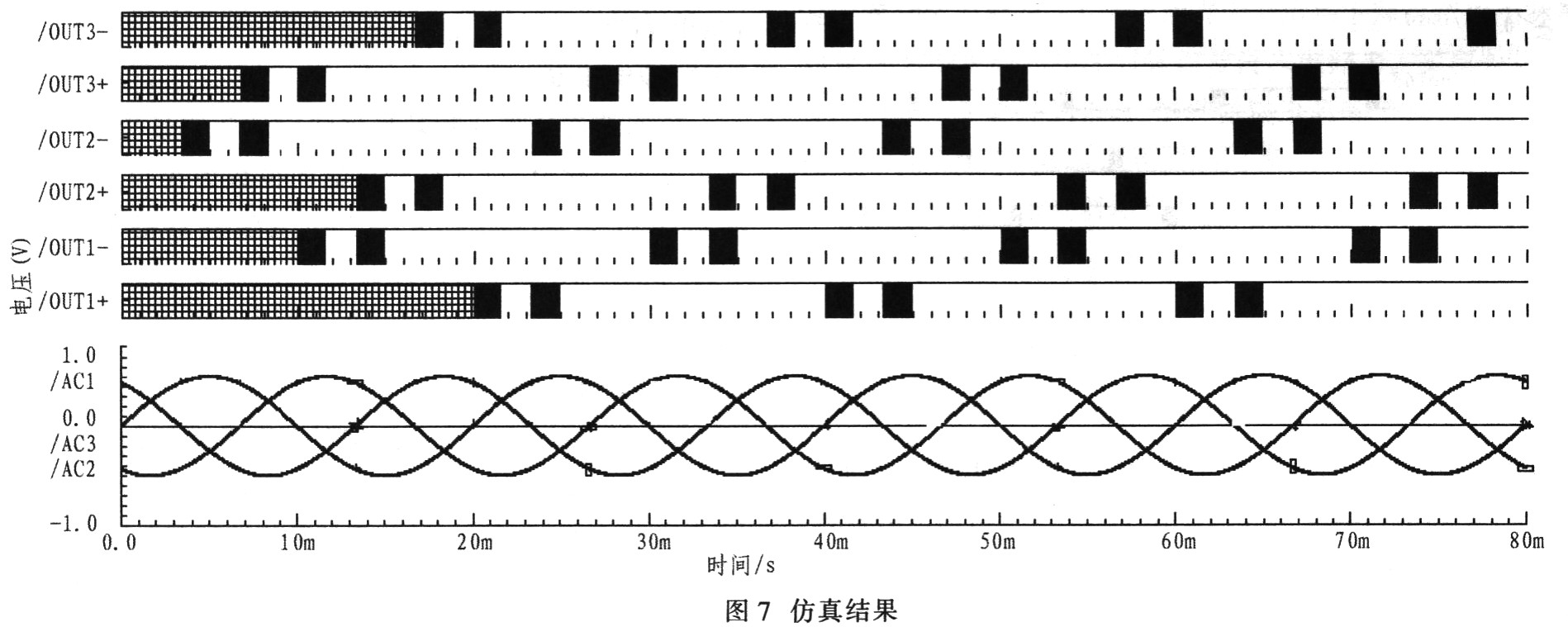

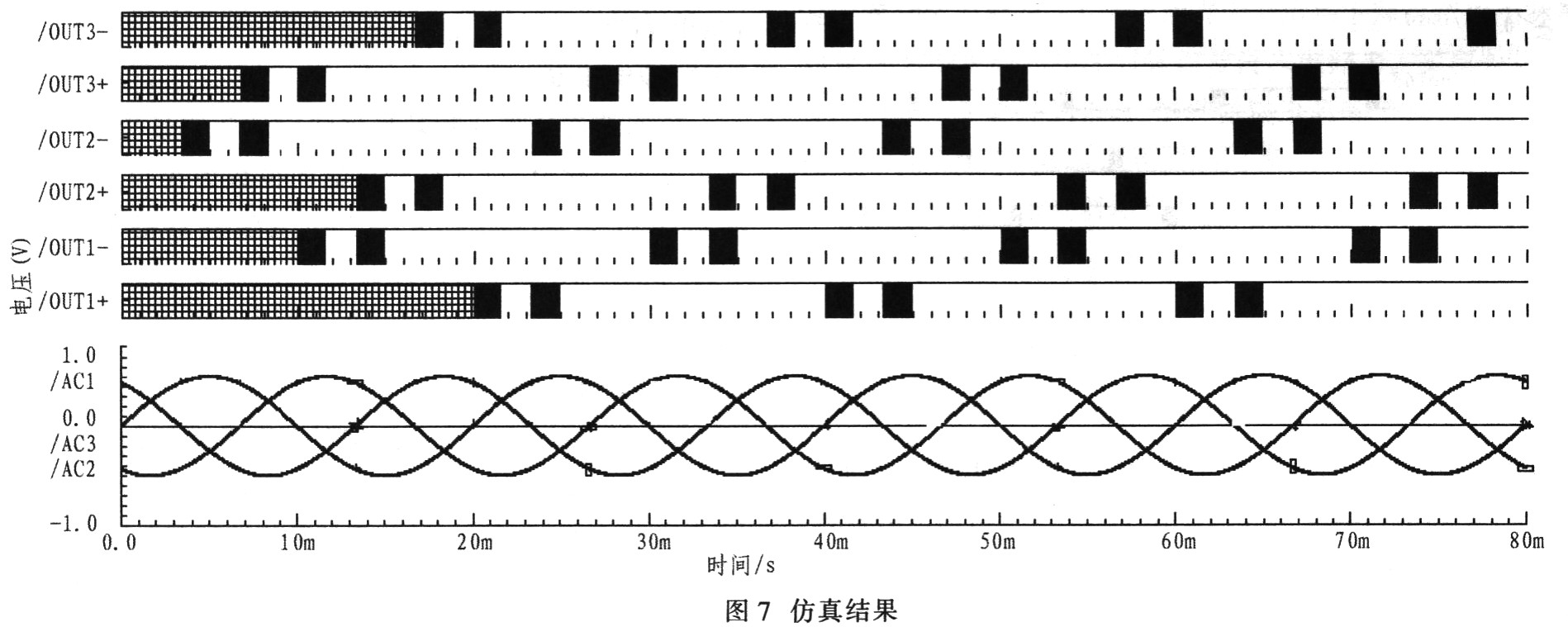

仿真结果如图7所示,输入为三相正弦信号,输出为6路移相触发脉冲。

3 测试结果

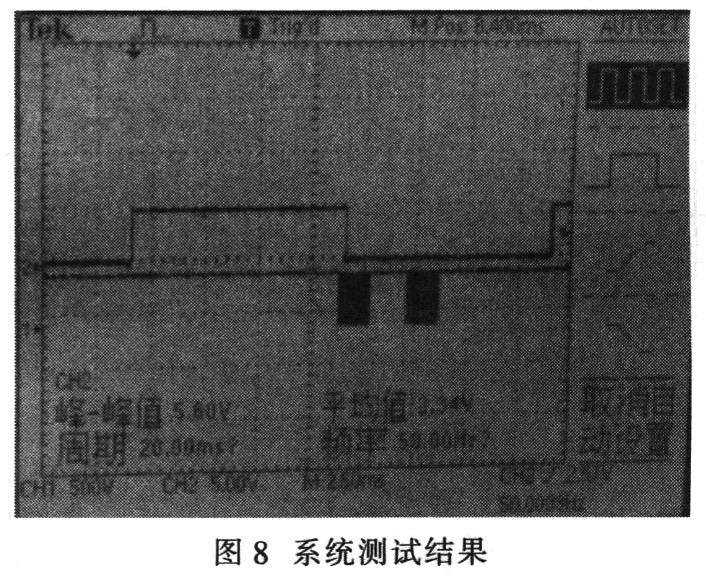

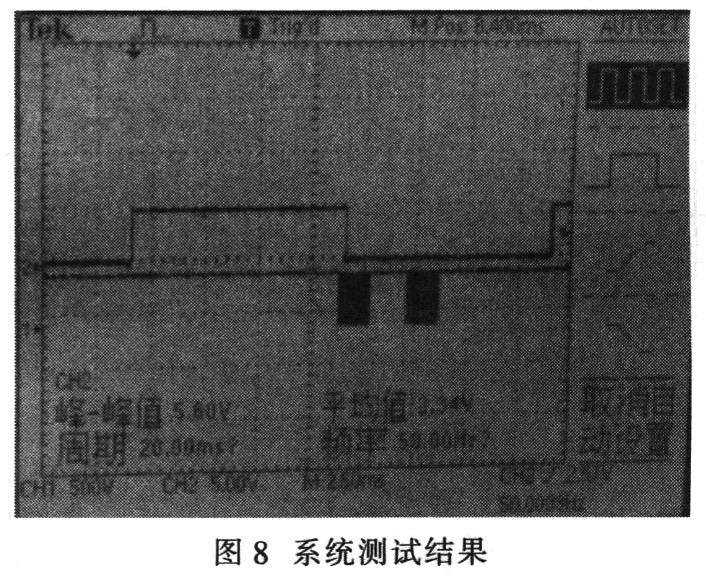

图8给出该系统测试结果。其中,其基本电参数测试结果如下:静态电源电流IDO<8 mA,输入端漏电流IIL<lμA,输入端漏电流IIH<lμA,输出吸收电0流IOL1(VOL=0.8 V)>25 mA,输出驱动电流IOH1(VOH=4 V)<一25 mA,输出吸收电流IOL2(VOL=0.5 V)>3 mA,高阻态漏电流IOZ<lμA。其功能测试结果为:移相范围为0~178°,移相精度为0.35°/mV。

4 结语

设计了一款用于可控硅控制的三相移相触发电路。针对点电网及现场出现的问题,提出了一种去抖动电路解决方案,给出了移相电路的基本设计思路。通过仿真和实际测试.该电路的移相范围达到178°,移相精度为0.35°/mV。该电路采用数字控制方式,使得移相精度和对称度大大提高,且控制方便,提高了电路的稳定性和可靠性,并克服以往电路精度差、可靠性低以及技术复杂等缺点。

移相触发集成电路采用1.2μm N阱双层多晶单层金属CMOS集成电路设计规则设计电路布局。采用全定制的布局设计方法。其特点是针对每个晶体管优化电路参数和布局以获得最佳性能以及最小面积。布局设计需解决的关键问题是减少衬底耦合噪声的影响,可通过以下途径解决:

(1)阱隔离环低掺杂的衬底中,物理隔离通过增加注入孔和感应孔间的距离来增加两者间的电阻,增强隔离效果。

(2)用P+扩散层形成隔离 P+扩散层通过吸收数字器件注入衬底的噪声电流达到隔离效果,隔离环用于包围数字电路或者是模拟电路。从另一个角度看,引入了P+隔离环后,减少环内的那部分衬底区域到地的电阻,也相应减小该区域受到的耦合噪声干扰。

(3)数字电路地与衬底分离将数字电路的N管的源极通过Metal接地,而不与衬底相连。衬底为模拟地,因此通过这种措施将模拟电路和数字电路地分开.模拟和数字电路通过地线耦合抑制噪声。

2.6 仿真结果

仿真结果如图7所示,输入为三相正弦信号,输出为6路移相触发脉冲。

3 测试结果

图8给出该系统测试结果。其中,其基本电参数测试结果如下:静态电源电流IDO<8 mA,输入端漏电流IIL<lμA,输入端漏电流IIH<lμA,输出吸收电0流IOL1(VOL=0.8 V)>25 mA,输出驱动电流IOH1(VOH=4 V)<一25 mA,输出吸收电流IOL2(VOL=0.5 V)>3 mA,高阻态漏电流IOZ<lμA。其功能测试结果为:移相范围为0~178°,移相精度为0.35°/mV。

4 结语

设计了一款用于可控硅控制的三相移相触发电路。针对点电网及现场出现的问题,提出了一种去抖动电路解决方案,给出了移相电路的基本设计思路。通过仿真和实际测试.该电路的移相范围达到178°,移相精度为0.35°/mV。该电路采用数字控制方式,使得移相精度和对称度大大提高,且控制方便,提高了电路的稳定性和可靠性,并克服以往电路精度差、可靠性低以及技术复杂等缺点。

可控硅 电路 电压 单片机 CPLD 集成电路 比较器 电阻 电容 振荡器 CMOS 电流 模拟电路 仿真 相关文章:

- 线性电源,可控硅电源,开关电源电路的简单比较(01-05)

- 交—交变频低频电源的研发与应用(05-26)

- 可控硅在红外遥控开关中的应用及工作原理(01-07)

- 基于MCU和基于ASIC的LED可控硅调光方案对比与解析(01-05)

- MB39C601:恒流AC-DC LED驱动器快速入门指南(08-09)

- MB39C601:恒流AC-DC LED驱动器从入门到精通(独家)(08-12)