Xilinx 20nm UltraScale架构助推无线电应用发展

时间:07-09

来源:互联网

点击:

- 关于滤波器和MAC

在任何DFE应用中,线性滤波器都是最常用的处理单元。在赛灵思 FPGA上集成此项功能后,建议[6]尽可能实现多通道滤波器,因为它的复合采样率(定义为通道数量与每条通道一般信号采样频率的乘积)与该设计运行所用的时钟速率相同。在所谓的并行架构中,每个DSP48 Slice根据数据通道支持单一滤波器系数,从而大幅简化了控制逻辑,并因此最大限度地降低设计资源利用率。

但是由于提高了时钟速率(例如,在最低速度等级UltraScale器件上时钟速率超过500 MHz),且滤波器以相对较低的采样率运行,因此通常会选择时钟速率作为复合采样率的倍数。可尽量提高时钟速率,以进一步减小设计占用的空间,同时降低功耗。在这种情况下,将需建立一个半并行架构,其中每个DSP48会根据通道处理K系数,而K是时钟速率与复合采样率之间的比率。最高效的实现方案包括将滤波器拆分为多个K相位,每个DSP48可处理这些K相位的一个特定系数。

在每个时钟周期中计算出连续多个滤波器输出相位,并将其累加形成一个输出样本(每个K周期一次)。因此,与并行实现方案相比,滤波器输出需要增加一个累加器。这种全精度累加器可作用于较大的数据宽度,等于bS+bC+bF,其中bS和bC分别表示数据样本的位宽度和系数,而bF=Log2N是滤波器的位增长,N是系数总数。因此,常规做法是在DSP48 Slice内实现累加器,以保证支持最高时钟速率并最大限度地降低占用空间和功率消耗。

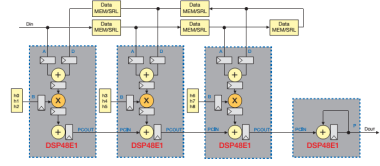

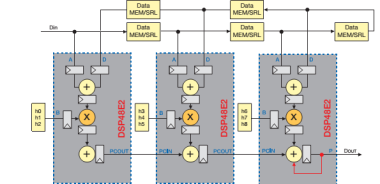

需要注意的是,各类滤波器都可以生成半并行架构,例如:单频率滤波器、整数型滤波器或分数率内插和抽取滤波器。图3是简化后的7系列和UltraScale实现方块图。图中清晰地突出了UltraScale解决方案的优势,由于其具备W-mux功能,相位累加器可被最后一个DSP48 Slice吸收。

(a)7 系列实现方案

(b)UltraScale实现方案

图3 – 在7 系列和UltraScale架构上实现半并行滤波器

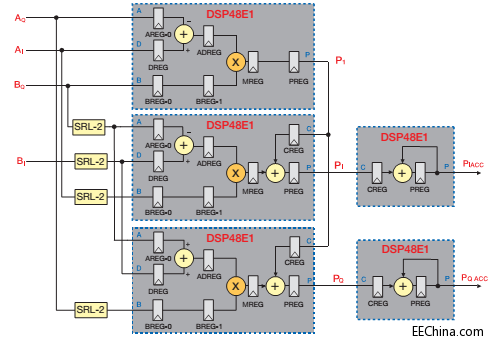

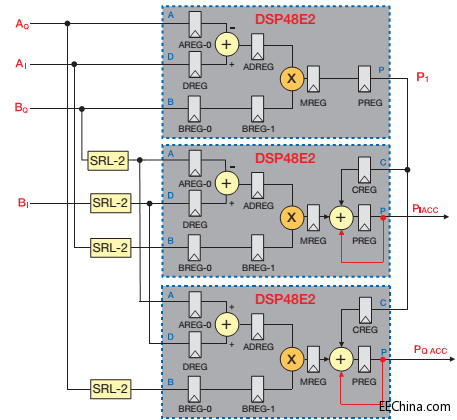

下面我们来思考一下如何实现每个时钟周期产生一个输出单元的全并行复合MAC运算符。众所周知,您可以重写复乘积的等式PI+j.PQ=(AI+j.AQ).(BI+j.BQ),从而根据以下等式仅使用三个真正的乘法运算:

- PI = P1 + AI.(BI - BQ)

- PQ = P1 + AQ.(BI + BQ)

(a)7 系列实现方案

(b)UltraScale实现方案

图4 – 在7 系列和UltraScale架构上实现复合MAC

因此,利用内置加法器,您只需三个DSP48(一个用于计算P1,另外两个用来处理PI和PQ输出)就能实现复合乘法器。根据延迟需求以及其中表述的速度性能指令,需要增加一些逻辑以在不同数据路径间平衡延迟。为获取最大速度支持,必须对DSP48实行完全流水线化,从而让运算符整个延迟六个周期。随后在每个输入端增加一个两周延迟线,让实际数据路径和虚构数据路径保持一致。在每个输入位配备四个SRL2,并利用SRL压缩功能将四个SRL2打包到两个LUT中。通过在每个PI和PQ输出端添加累加器来最终完成复合MAC。此外,这个累加器会作用于较大的数据宽度,因此能更好地集成到DSP48 Slice中。图4显示7 系列和UltraScale器件相应的实现方案,从而再一次展示了W-mux集成的优势。PI和PQ DSP48E2 Slice在吸收累加器时可节省40%资源。值得一提的是,该方式还减少了延迟,对一些应用十分有益。

您可以用类似结构构建带有三个真实滤波器的复合滤波器(其中一个具备复合数据和系数),如图5所示。输入信号的真实部分和虚构部分会馈送至两个真实滤波器中,其系数分别为该滤波器系数虚构部分和真实部分的差值和总和。第三个滤波器用系数的真实部分处理并行的输入端真实与虚构部分的总和。当需要建立并行滤波器时,最终可将三个滤波器的输出端结合起来,以生成输出端的真实与虚构组件,其将再次受益于W-mux,这也是DFE应用中使用均衡器的典型状况。

图5 – 复合滤波器的实现架构

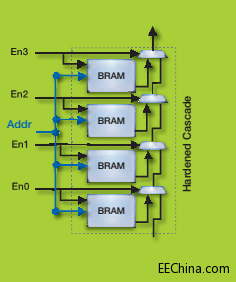

图6 – UltraScale器件上的BRAM级联

UltraScale内存架构的优势

UltraScale器件集成的Block RAM与7 系列中集成的Block RAM基本相同,但新架构引入了硬件数据级联方案以及动态电源门控能力。图6显示了该级联,其中展示的是同一列中在每个上下相邻的Block RAM间嵌入的数据多路复用器。因此,无需使用其它逻辑资源便能以由下至上的方式建立更大内存。

该级联覆盖了器件上的所有整列,但最好将级联的使用限制在单个时钟区域(即12个连续BRAM)以避免时钟偏移并最大限度提升时序性能。此外,它还提供足够的灵活性,可支持该级联功能的不同实现。实际上,您既可以将多路复用器应用到位于可选寄存器前后的Block RAM数据输入端,也可以用于数据输出端。

该级联使建立需要多个BRAM的大型内存成为可能,同时占用空间极少,支持最高时钟速率以及最低功率消耗,而这些在7 系列器件上则无法实现。比如,在7 Se系列器件上,通过配置为16K×2位的八个BRAM(36K)实现存储16位数据的16K内存,以避免外部数据复用,而这样则需要增加逻辑资源和延迟,并会影响计时与布线拥塞。从动态功率角度来说,这种方法效率较低,因为在所有读取或写入操作中都要启 动这八个Block RAM。最佳解决方案包括使用2Kx16位配置,由于这样只需启动一个BRAM,因此消耗的动态功率只有上述方法的八分之一。级联功能连同动态功率门控功能正好可以在UltraScale器件上实现这种效果。

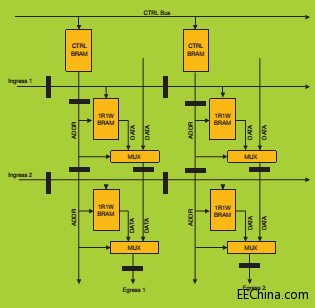

Block RAM级联的另一种直接应用与实现I/Q数据转换功能有关,通常与DFE系统的基带CPRI接口集成。图7展示了通常由一个NxM存储器阵列组成的高级交换架构。N入口流上的连续数据会根据其输出目的地写入到相应的Block RAM中并形成一行,且会从相应的Block RAM以一列的形式读取M出口流。因此,可以用BRAM级联有效实现每一列。

如欲了解有关20nmUltraScale系列的更多信息,敬请访问http://china.xilinx.com/products/silicon-devices/fpga/index.htm。

图7 – 数据交换高级架构

赛灵思 无线电 DSP FPGA SoC DAC ADC 滤波器 ARM Cortex 相关文章:

- 赛灵思为以太网AVB网络流媒体传输推出高服务质量连接解决方案(01-12)

- 赛灵思扩大生态系统,重塑嵌入式视觉、工业物联网系统设计的未来(04-24)

- 基于赛灵思FPGA的数字频域干扰抵消器(11-23)

- 基于Virtex-5的串行传输系统设计与验证(12-24)

- 利用串行RapidIO交换机设计模块化无线基础系统(03-12)

- 一种可编程ExpressCard解决方案(07-15)