SOC芯片设计与测试

时间:08-02

来源:互联网

点击:

结论

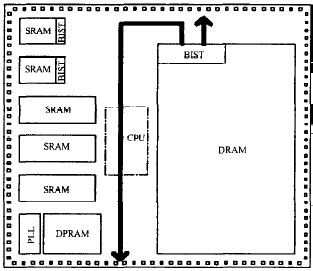

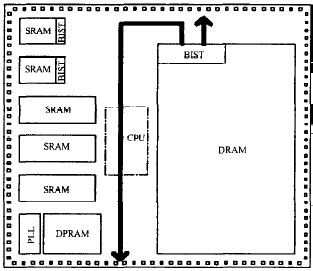

本芯片系统包含了嵌入式DRAM、大容量的SRAM、模拟模块、专用数字逻辑,因此生产测试面临着极大挑战。在设计时根据具体情况,通过面向测试设计DFT和面向可生产性的设计DFM,针对各模块得出一个多样化的解决策略。最终,用标准的IEEE1149.1接口构造器件进入不同的测试模式

图5 DRAM测试结构

本芯片系统包含了嵌入式DRAM、大容量的SRAM、模拟模块、专用数字逻辑,因此生产测试面临着极大挑战。在设计时根据具体情况,通过面向测试设计DFT和面向可生产性的设计DFM,针对各模块得出一个多样化的解决策略。最终,用标准的IEEE1149.1接口构造器件进入不同的测试模式

图5 DRAM测试结构

DSP ADC DAC 电路 嵌入式 PWM 总线 电压 电源管理 电流 振荡器 CSR 相关文章:

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)