SOC芯片设计与测试

时间:08-02

来源:互联网

点击:

以往的系统设计是将CPU,DSP,PLL,ADC,DAC或Memory等电路设计成IC后,再加以组合变成完整的系统,但现今的设计方式是将上述的电路直接设计在同一个IC上,或购买不同厂商的IP(intellectual property),直接加以整合,此方式称为单晶片片上系统(SOC)设计方法。SOC方式大大降低了昂贵的设计和制造成本,但对于测试来说却变得更为复杂,测试成本也越来越高,测试问题已不容忽视。面向测试设计(DFT)及面向生产设计(DFM)已越来越得到高度重视。因此,在SOC设计时,必须考虑产品测试。

复杂SOC器件是对测试经济学的挑战。随着工艺进步,器件越来越小;而随着功能增加,测试复杂度却不断上升。SOC产品在生产测试时对测试仪的要求也越来越高,昂贵的测试成本已在制造过程中占很大的比例。考虑成本要求,一般只允许在几秒或更少的时间内完成测试。由于典型的DRAM都有比较长的测试时间,因此嵌入式的DRAM测试更具挑战性。设计时除了考虑测试成本,还要求必须便于测试分析。

DFT是基于IEEE1149.1的JTAG控制。除了专门的存储器测试和ATPG扫描测试,JTAG控制器还针对产品中的不同单元模块提供各种不同的试模式。这里介绍的DFT和DFM包括用于加速设计分析和合格率研究的面向测试设计及用于降低测试成本的并行测试设计。

单芯片系统介绍

微控制器CPU:是C163系列的16位控制器,此外还带有累加器(MAC)、通用定时器(GPT)、同步与异步序列控制器(ASC,SSC)和脉冲宽度调制器(PWM)等。为便于从一种应用转为其他应用,整个控制器由逻辑综合完成。硬盘控制器HDC:HDC大约由250K的“与非门”组成。HDC的主要特点在于有强大的省电模式,即每一功能块可被独立地切换或将时钟降低8倍。根据ATA规范,HDC有不同的省电模式:运行、空闲模式1、空闲模式2、待机、休眠等。这使SOC的功耗从270mW下降到54mW。大容量SRAM:片内集成了80K字节的程序SRAM、8K字节的数据SRAM和直接与微处理器相连的2K字节的双端口SRAM。

缓冲存储器DRAM:整个芯片的中心部分是嵌入式DRAM,是一个8兆位的缓冲存储器。片上DRAM不需要外部数据总线即能存取程序和数据,而功耗只是最大运行模式下的十分之一。

PLL:片上所有的时钟频率是由400MHz的PLL产生的。PLL为全定制单元,测试模式由JTAG控制器控制。

PVT单元:用于指示环境温度,监视动态环境(温度和电压)变化及HDC逻辑,并自动调整ATA的端口参数。PVT单元是全定制的,测试模式由JTAG控制。

电源管理:SOC内集成了电压调整的控制电路。调节器可以提供从核心电路所需的1.8V到I/O口所需的3.3V电压。一个外部晶体管用于处理所有核心逻辑所需的电流。片内包含一个驱动外部晶体管的整流控制电路。整流器是全定制的,其测试模式由JTAG控制。

测试设计分析

由于存储器占了45%的芯片面积、86%的晶体管数,同时由于DRAM的时序特性,既便单个存储器单元比逻辑门小得多,测试一个DRAM单元也要比测试一个“与”门需要更多的时间。因此需要特别关注存储器测试,这也是业界聚焦和努力的方向。根据SRAM在系统中的不同作用,可以利用微控制器测试或通过MBIST电路完成测试。

SOC上的DRAM可通过一个BIST控制器测试,而DRAMBIST电路自身则通过“扫描”和ATPG进行测试。大部分的数字逻辑是综合而成,因此均可通过ATPG扫描进行测试。为了有效降低测试时间,改善DRAM的DFT测试开发是最有益处的,设计时尽量考虑并行测试。同时,像振荡器和PLL等模拟单元也应在一个合理的时间内完成测试。另外,当进行ATPG或扫描测试时,测试还受到自动测试设备(ATE)内部的测试向量存储器容量的制约,设计时需事先考虑。

DFT和DFM的测试实现

由于器件比较复杂,对于不同的功能模块采用了不同的测试结构。

ATPG扫描测试

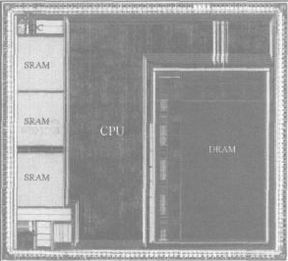

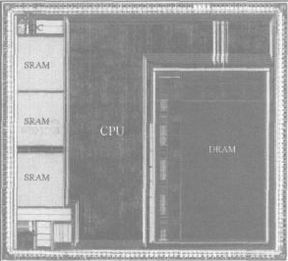

扫描结构如图2所示。为了可在ATE测试仪上进行多器件并行扫描测试,扫描链的输入端被设计在芯片相对的两边。器件的特殊之处在于它包含了多路的级敏扫描(LSSD)电路。DRAM的BIST就是LSSD扫描,由工艺厂家提供,而其余的设计尽量使用标准的多路扫描触发器。在LSSD扫描电路和多路扫描逻辑中,没有插入隔离逻辑。由于LSSD与多路扫描之间不同的时序,在设计时,LSSD与多路扫描的合成可能会遇到问题,即可能出现对某些触发器采样时,数据不确定性而导致失现以某一SOC产品为例进行介绍。器件由0.18?m的铜工艺制造,有很好的性能和极低的功耗。芯片系统主要部分组成见图1。

图1 芯片版图

图2 扫描模式结构

效覆盖率的损失。因此在设计时应特别关注两者的匹配。

考虑到在进行扫描测试时,某些不需要的模式可能会激活,而逻辑电路只占用整个芯片面积的很小部分,因此经过折中后,考虑了增加电路部分的成本与测试覆盖率之间的关系,有一小部分电路没有被扫描。由于逻辑电路只占用整个芯片面积的很小部分,因此,对于整个器件来说,减小逻辑的失效覆盖率是可以接受的。经验证,逻辑的单固定型故障覆盖率在95%。

复杂SOC器件是对测试经济学的挑战。随着工艺进步,器件越来越小;而随着功能增加,测试复杂度却不断上升。SOC产品在生产测试时对测试仪的要求也越来越高,昂贵的测试成本已在制造过程中占很大的比例。考虑成本要求,一般只允许在几秒或更少的时间内完成测试。由于典型的DRAM都有比较长的测试时间,因此嵌入式的DRAM测试更具挑战性。设计时除了考虑测试成本,还要求必须便于测试分析。

DFT是基于IEEE1149.1的JTAG控制。除了专门的存储器测试和ATPG扫描测试,JTAG控制器还针对产品中的不同单元模块提供各种不同的试模式。这里介绍的DFT和DFM包括用于加速设计分析和合格率研究的面向测试设计及用于降低测试成本的并行测试设计。

单芯片系统介绍

微控制器CPU:是C163系列的16位控制器,此外还带有累加器(MAC)、通用定时器(GPT)、同步与异步序列控制器(ASC,SSC)和脉冲宽度调制器(PWM)等。为便于从一种应用转为其他应用,整个控制器由逻辑综合完成。硬盘控制器HDC:HDC大约由250K的“与非门”组成。HDC的主要特点在于有强大的省电模式,即每一功能块可被独立地切换或将时钟降低8倍。根据ATA规范,HDC有不同的省电模式:运行、空闲模式1、空闲模式2、待机、休眠等。这使SOC的功耗从270mW下降到54mW。大容量SRAM:片内集成了80K字节的程序SRAM、8K字节的数据SRAM和直接与微处理器相连的2K字节的双端口SRAM。

缓冲存储器DRAM:整个芯片的中心部分是嵌入式DRAM,是一个8兆位的缓冲存储器。片上DRAM不需要外部数据总线即能存取程序和数据,而功耗只是最大运行模式下的十分之一。

PLL:片上所有的时钟频率是由400MHz的PLL产生的。PLL为全定制单元,测试模式由JTAG控制器控制。

PVT单元:用于指示环境温度,监视动态环境(温度和电压)变化及HDC逻辑,并自动调整ATA的端口参数。PVT单元是全定制的,测试模式由JTAG控制。

电源管理:SOC内集成了电压调整的控制电路。调节器可以提供从核心电路所需的1.8V到I/O口所需的3.3V电压。一个外部晶体管用于处理所有核心逻辑所需的电流。片内包含一个驱动外部晶体管的整流控制电路。整流器是全定制的,其测试模式由JTAG控制。

测试设计分析

由于存储器占了45%的芯片面积、86%的晶体管数,同时由于DRAM的时序特性,既便单个存储器单元比逻辑门小得多,测试一个DRAM单元也要比测试一个“与”门需要更多的时间。因此需要特别关注存储器测试,这也是业界聚焦和努力的方向。根据SRAM在系统中的不同作用,可以利用微控制器测试或通过MBIST电路完成测试。

SOC上的DRAM可通过一个BIST控制器测试,而DRAMBIST电路自身则通过“扫描”和ATPG进行测试。大部分的数字逻辑是综合而成,因此均可通过ATPG扫描进行测试。为了有效降低测试时间,改善DRAM的DFT测试开发是最有益处的,设计时尽量考虑并行测试。同时,像振荡器和PLL等模拟单元也应在一个合理的时间内完成测试。另外,当进行ATPG或扫描测试时,测试还受到自动测试设备(ATE)内部的测试向量存储器容量的制约,设计时需事先考虑。

DFT和DFM的测试实现

由于器件比较复杂,对于不同的功能模块采用了不同的测试结构。

ATPG扫描测试

扫描结构如图2所示。为了可在ATE测试仪上进行多器件并行扫描测试,扫描链的输入端被设计在芯片相对的两边。器件的特殊之处在于它包含了多路的级敏扫描(LSSD)电路。DRAM的BIST就是LSSD扫描,由工艺厂家提供,而其余的设计尽量使用标准的多路扫描触发器。在LSSD扫描电路和多路扫描逻辑中,没有插入隔离逻辑。由于LSSD与多路扫描之间不同的时序,在设计时,LSSD与多路扫描的合成可能会遇到问题,即可能出现对某些触发器采样时,数据不确定性而导致失现以某一SOC产品为例进行介绍。器件由0.18?m的铜工艺制造,有很好的性能和极低的功耗。芯片系统主要部分组成见图1。

图1 芯片版图

图2 扫描模式结构

效覆盖率的损失。因此在设计时应特别关注两者的匹配。

考虑到在进行扫描测试时,某些不需要的模式可能会激活,而逻辑电路只占用整个芯片面积的很小部分,因此经过折中后,考虑了增加电路部分的成本与测试覆盖率之间的关系,有一小部分电路没有被扫描。由于逻辑电路只占用整个芯片面积的很小部分,因此,对于整个器件来说,减小逻辑的失效覆盖率是可以接受的。经验证,逻辑的单固定型故障覆盖率在95%。

DSP ADC DAC 电路 嵌入式 PWM 总线 电压 电源管理 电流 振荡器 CSR 相关文章:

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)