SOC芯片设计与测试

时间:08-02

来源:互联网

点击:

SRAM测试

片内有两种SRAM:一是与微处理器(数据,代码存储器)紧密联系的CPUSRAM;另一种是硬盘控制使用的HDCSRAM,不能被微控制器直接读取,为双端口SRAM。两者分别采用了不同的测试策略。

CPUSRAM测试策略

如密集SRAM一样,SRAM宏单元的版图也是用手工优化完成,这样可以不断接近工艺极限,节省空间和能耗。为了获得更高的产出率,密集的SRAM中加入了冗余单元。为了降低测试成本,尽量减少了插入电路。大部分的测试由片上DRAM存储器激励,可在存储器测试仪上直接测试。考虑到SRAM测试要在存储器测试仪上运行,因此,在设计时把微控制器读取存储器模块SRAM的测试算法存储在一个叫MSIST(存储器自检软件)的ROM里。这个程序不仅可以很容易被存储器测试仪控制,而且很容易通过单层掩膜重设计完成更改变动。

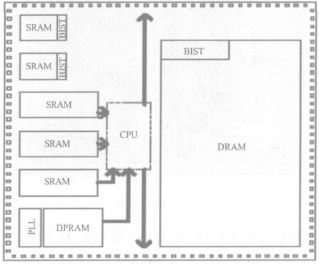

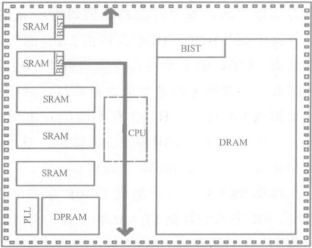

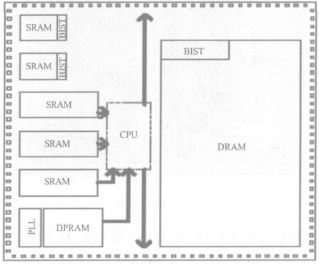

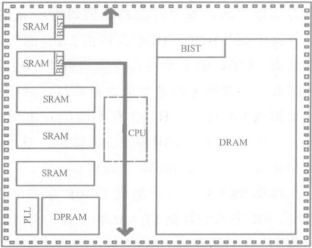

测试结构见图3。HDC中的小模块无法被微处理器核测试,必须用图4中的MBIST(存储器内建自测试)的结构测试。通过这样的DFT设计,就可以在一个专用存储器测试仪上完成所有的存储器测试,继而进行冗余存储器的熔断。MSIST和MBIST可以执行march-14,棋盘测试和反棋盘等测试。

图3 MSIST 结构

图4 MBIST 结构

双端口SRAM的BIST软件测试:

芯片内不能被CPU直接读取的HDC双端口SRAM,则通过CPU运行BIST算法由下载软件完成测试。由于采用软件测试方法,需要花精力准备软件测试向量,在设计时,应考虑SRAM的版图及片上MBIST逻辑的建立。

对大多数SRAM来说,MBIST运行速度与功能存储采用同样的方法和速度,而硬件MBIST常常在较低速度或修改访问后综合而成。因此用软件方法不会出现在测试时RAM通过,而在实际应用时失效等现象。

DFM:

测试时应考虑为所有的SRAM创建一张位失效图(BFM),可通过CPU的数据线输出。这些位失效图对生产制造很重要,在合格率研究和改善方面,可以给工艺工程师提供极其重要和必要的信息。

DRAM测试

在过去的几年里,嵌入式DRAM的测试是关注的焦点。熔断前测试是通过特殊的逻辑从引脚加入的。外部ATE存储器提供所有的激励和期望结果比较,并由ATE对失效单元建立BFM及计算最佳修复方案。DRAMBIST有能力自建冗余计算,也就是BISR(内建自修复),但为了减少测试时间,本案不使用此功能。BIST逻辑自身用ATPG和LSSD扫描寄存器测试。

高并行测试的DRAM结构

通常,DRAM占用的测试时间比逻辑测试长。因此为了降低单个器件的有效测试时间,设计时考虑了高并行测试。

嵌入式DRAM的熔断前测试是在一个专用存储器测试仪上进行,使用BIST的直通模式(图5)。这样,通过降低冗余修复的计算时间及高并行测试减少了测试时间。一个专用存储器测试仪的优点是:硬件支持存储器测试算法、能对一个完整的多兆位存储器进行位失效信息的存储和分析,以及并为高并行测试提供大量的供电电源。

本器件选用存储器ATE进行测试。因此,需要一个最小测试模式导入(准备序列)来构造存储器。一旦存储器构造好,还需提供一个典型的存储器接口,包括冗余数据输入和输出的导入。通过限制地址和数据输入的数量,并且将所需的引脚分列在芯片的两相对边沿,可以实现高并行测试。

带有BIST的DRAM测试

有BIST控制器的DRAM模块,能在IEEE1149.1指令合理配置后被激活(图5)。一旦熔丝开始,DRAM测试就不需要专门考虑存储器的修复,而可在标准的逻辑ATE上进行。因为BIST由片上产生地址和控制信号,并只送出一个通过/失效结果。所以,用于连接的端口数将大大减少。

DFM

可制造性设计的原则引导着DRAM的分析设计开发。焦点不是在限制引脚的数量和位置,而在于尽量为嵌入式存储器提供尽量多的可控制性和可观察点。通过JTAG控制器,可以选择一个最小测试模式导入序列,使用更多的控制线和数据线,包括芯片上所有边缘的引脚。这种模式是用于失效分析而不用于生产测试。像SRAM一样,DRAM测试也应创建位失效图,并传送到ATE做近一步分析。

独特的DFM特点:环形振荡器

芯片内设计了两个在生产时用于加速测量的环形振荡器。这些环形振荡器有2ns的自然周期,每个与32分频的逻辑相连。典型的对外周期是64ns,用标准ATE就可以产生适于测量的频率。为了比较连线和门延时的影响,用了两种版图布线方法。一个环形振荡器用密集布线;另一个用人工布线。环形振荡器的测量结果反映了硅片速度,可以用来跟踪工艺变化,以消除器件太快或太慢。

片内有两种SRAM:一是与微处理器(数据,代码存储器)紧密联系的CPUSRAM;另一种是硬盘控制使用的HDCSRAM,不能被微控制器直接读取,为双端口SRAM。两者分别采用了不同的测试策略。

CPUSRAM测试策略

如密集SRAM一样,SRAM宏单元的版图也是用手工优化完成,这样可以不断接近工艺极限,节省空间和能耗。为了获得更高的产出率,密集的SRAM中加入了冗余单元。为了降低测试成本,尽量减少了插入电路。大部分的测试由片上DRAM存储器激励,可在存储器测试仪上直接测试。考虑到SRAM测试要在存储器测试仪上运行,因此,在设计时把微控制器读取存储器模块SRAM的测试算法存储在一个叫MSIST(存储器自检软件)的ROM里。这个程序不仅可以很容易被存储器测试仪控制,而且很容易通过单层掩膜重设计完成更改变动。

测试结构见图3。HDC中的小模块无法被微处理器核测试,必须用图4中的MBIST(存储器内建自测试)的结构测试。通过这样的DFT设计,就可以在一个专用存储器测试仪上完成所有的存储器测试,继而进行冗余存储器的熔断。MSIST和MBIST可以执行march-14,棋盘测试和反棋盘等测试。

图3 MSIST 结构

图4 MBIST 结构

双端口SRAM的BIST软件测试:

芯片内不能被CPU直接读取的HDC双端口SRAM,则通过CPU运行BIST算法由下载软件完成测试。由于采用软件测试方法,需要花精力准备软件测试向量,在设计时,应考虑SRAM的版图及片上MBIST逻辑的建立。

对大多数SRAM来说,MBIST运行速度与功能存储采用同样的方法和速度,而硬件MBIST常常在较低速度或修改访问后综合而成。因此用软件方法不会出现在测试时RAM通过,而在实际应用时失效等现象。

DFM:

测试时应考虑为所有的SRAM创建一张位失效图(BFM),可通过CPU的数据线输出。这些位失效图对生产制造很重要,在合格率研究和改善方面,可以给工艺工程师提供极其重要和必要的信息。

DRAM测试

在过去的几年里,嵌入式DRAM的测试是关注的焦点。熔断前测试是通过特殊的逻辑从引脚加入的。外部ATE存储器提供所有的激励和期望结果比较,并由ATE对失效单元建立BFM及计算最佳修复方案。DRAMBIST有能力自建冗余计算,也就是BISR(内建自修复),但为了减少测试时间,本案不使用此功能。BIST逻辑自身用ATPG和LSSD扫描寄存器测试。

高并行测试的DRAM结构

通常,DRAM占用的测试时间比逻辑测试长。因此为了降低单个器件的有效测试时间,设计时考虑了高并行测试。

嵌入式DRAM的熔断前测试是在一个专用存储器测试仪上进行,使用BIST的直通模式(图5)。这样,通过降低冗余修复的计算时间及高并行测试减少了测试时间。一个专用存储器测试仪的优点是:硬件支持存储器测试算法、能对一个完整的多兆位存储器进行位失效信息的存储和分析,以及并为高并行测试提供大量的供电电源。

本器件选用存储器ATE进行测试。因此,需要一个最小测试模式导入(准备序列)来构造存储器。一旦存储器构造好,还需提供一个典型的存储器接口,包括冗余数据输入和输出的导入。通过限制地址和数据输入的数量,并且将所需的引脚分列在芯片的两相对边沿,可以实现高并行测试。

带有BIST的DRAM测试

有BIST控制器的DRAM模块,能在IEEE1149.1指令合理配置后被激活(图5)。一旦熔丝开始,DRAM测试就不需要专门考虑存储器的修复,而可在标准的逻辑ATE上进行。因为BIST由片上产生地址和控制信号,并只送出一个通过/失效结果。所以,用于连接的端口数将大大减少。

DFM

可制造性设计的原则引导着DRAM的分析设计开发。焦点不是在限制引脚的数量和位置,而在于尽量为嵌入式存储器提供尽量多的可控制性和可观察点。通过JTAG控制器,可以选择一个最小测试模式导入序列,使用更多的控制线和数据线,包括芯片上所有边缘的引脚。这种模式是用于失效分析而不用于生产测试。像SRAM一样,DRAM测试也应创建位失效图,并传送到ATE做近一步分析。

独特的DFM特点:环形振荡器

芯片内设计了两个在生产时用于加速测量的环形振荡器。这些环形振荡器有2ns的自然周期,每个与32分频的逻辑相连。典型的对外周期是64ns,用标准ATE就可以产生适于测量的频率。为了比较连线和门延时的影响,用了两种版图布线方法。一个环形振荡器用密集布线;另一个用人工布线。环形振荡器的测量结果反映了硅片速度,可以用来跟踪工艺变化,以消除器件太快或太慢。

DSP ADC DAC 电路 嵌入式 PWM 总线 电压 电源管理 电流 振荡器 CSR 相关文章:

- 基于IXP421的VoIP网关及其性能测评(10-02)

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)