基于IXP421的VoIP网关及其性能测评

作者: 广东高新兴通信设备有限公司

清华大学电子工程系 姚启欣,唐昆,黄稳

摘 要:本文简要介绍了基于IXP421的语音网关的系统结构,以及语音DSP模块的工作原理。系统中没有专用的语音DSP,而是由IXP421的XSCALE核实现。系统软件、应用软件和语音DSP共享CPU时间。语音处理能力会受到编码方式和CPU负荷的制约,因此,本文通过实际系统的测试结果对Intel公司声明的性能指标进行了验证。

关键词:VoIP;DSP;XSCALE;编解码

引言

就VoIP设备来说,如果语音处理器的功能和其它应用功能由一个处理器来完成,必然能极大地简化电路,降低成本。Intel的IXP421即是这些多功能处理器的其中一种,它的PCM接口使VoIP设备的硬件结构大大简化了,还可以通过选择不同微代码的方式实现更加灵活的网络应用。

Intel提供的解决方案是通过软件DSP实现语音处理,并声明DSP模块可同时处理四路PCM窄带话音,支持多种语音编码及回波消除等功能。众所周知,单路单向PCM语音速率为64Kbps,单路双向为128Kbps,4路双向则为512Kbps,如何保证语音处理所需要的CPU时间是个关键问题。

另外,回波消除或其它附加功能也会增加处理时间,在设计中还要考虑内存读写、任务切换、中断处理等系统因素造成的影响。

IXP421简介

IXP421是Intel公司开发的采用XSCALE内核的IXP4xx系列处理器之一,主频为266MHz。IXP421采用多处理引擎和硬件多线程处理机制。它包括了一个处理器内核和两个并行网络处理引擎,其中XSCALE内核为处理器核心,它是以ARM V5内核为原型,进行了DSP功能扩展,并优化了16位数据类型的累加和乘法运算。启动时首先初始化XSCALE核,然后网络处理引擎将从内存下载各自的微代码,以完成外围网络接口的链路层协议处理,它们的执行是完全并行于XSCALE内核的,通过内嵌的消息队列与XSCALE核同步。先进高速总线(AHB)实现网络处理引擎和XSCALE核之间的数据交换,其传输速率达到133.32MHz×32bit,完全能够满足高速网络的数据传输要求。

DSP软件模块

Intel公司为IXP4xx系列处理器专门开发了DSP软件包。根据实现的不同功能,运行时的DSP模块可分为几个部分,包括网络端点、编码器、解码器、音频生成器、音频检测器、语音播放器、混音器和T.38。如果系统有四路电话,则每一路电话应该分配一个网络端点,一个音频生成器,一个音频检测器,网络端点代表每一路电话所需的TDM前端处理功能,用以实现TDM数据的收发、发送增益控制和回波消除,而音频生成器、音频检测器则分别实现每一路电话的提示音及DTMF音频检测功能。另外,各路电话分享一个编码器和一个解码器,语音分流器负责控制网络端点和编解码器之间的数据流。语音播放器和混音器可多路共用,也可各路单独占用一个,具体个数由应用需求决定。

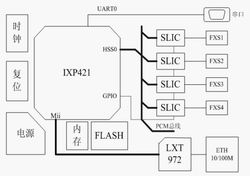

图1 系统硬件结构 系统结构整个系统由用户线接口、以太网接口、处理器和通信控制总线组成,如图1所示。处理器即IXP421,它是设备运行的嵌入式操作系统及应用程序的载体,主要功能是:在通话过程中充当语音数字处理器并分发语音包给特定的终端;在呼叫建立过程中处理网络协议;初始化并控制各部分硬件模块协同工作;提供用户管理界面。内存芯片容量为64MB,通过PC133内存总线连接IXP421的内存控制器。16MB的Intel Strata Flash芯片通过扩展总线连接IXP421。时钟电路为处理器提供频率为33.33MHz的参照时钟,处理器内核及其集成外围电路的时钟均由此分频得到。复位电路为处理器提供上电复位功能,即在系统加电并稳定后复位引脚,保持至少500ms的低电平。 用户线接口,以Silicon Laboratroies公司的Si3210型接口芯片为核心,为用户提供模拟电话接口功能,这些功能包括:用户线直流馈电、摘挂机状态检测、DTMF检测、振铃、回铃音及各种提示音、音频采样及D/A、A/D转换,以及PCM数据收发等。 以太网接口,采用Intel的以太网接口芯片LXT972,其主要功能有:10BASE-T/100BASE-TX自适应、自动网络协商、冲突检测、链路状态告警,通过MII总线接口,配合IXP421的以太网处理引擎(NPE),实现链路层功能,承载TCP/IP协议及其它应用层网络协议。 串口,为用户提供基于串口的管理及调试功能。IXP421有两组串行输入、输出接口,分别为UART0和UART1,其中UART0是高速串行通信端口,支持的通信波特率最高达921.6Kbps。UART1为CONSOLE串行通信口,支持的波特率范围为1200bps~231Kbps。 系统中较为重要的外部总线的作用如下: 1. HSS(High Speed Serial)总线,连接处理器的WAN/语音NPE和用户线接口芯片(SLIC),有时钟、帧同步、输入、输出4条线,支持同步串行传输,可配置时钟频率范围为512KHz~8.192MHz。本文应用作为PCM语音信号的传输总线,时钟为2MHz,即总共支持32个时隙。4路SLIC芯片各占一个时隙进行通信。IXP421的一个专用协处理器(VOICE NPE)负责HSS端口的总线数据收发。 2. MII(Media Independent Interface)总线,连接处理器的以太网NPE和以太网PHY接口芯片LXT972,分为MII数据总线和MII管理信息总线。IXP421的网络处理引擎(NPEA)通过MII收发数据,网络处理引擎独立于主CPU内核工作,采用硬件多线程机制,使数据收发不占用主处理器时间,NPEA运行的微程序可提供对以太网PHY设备的简单控制功能。 3. 控制用户线接口芯片的串行外围接口SPI(Serial Peripheral Interface)以菊花链形式串接,有输入、输出、时钟、片选4根线,占用处理器的4个GPIO引脚。以串行8位命令方式读写SLIC的内部寄存器,可以看作SLIC的控制总线。 |

- 新一代移动通信系统的关键技术(10-26)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 设计基于TMS320LF2407的低功耗中文人机界面 (04-16)

- USB接口芯片的原理及应用 (04-15)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)