PLL锁相环的基本结构及工作原理

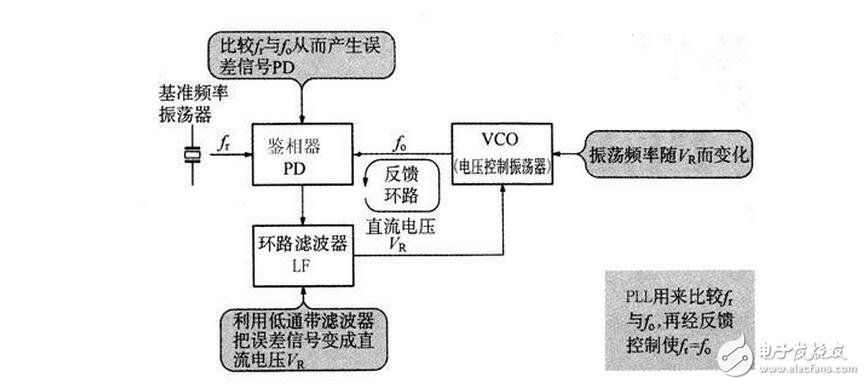

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,有相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时脉冲讯号。

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

一个典型的锁相环(PLL)系统,是由鉴相器(PD),压控荡器(VCO)和低通滤波器(LPF)三个基本电路组成,如图

锁相环路的捕捉与跟踪过程

当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。锁相环由失锁到锁定的过程,人们称为捕捉过程。系统能捕捉的最大频率范围或最大固有频带称为捕捉带或捕捉范围。

当锁相环路锁定后,由于某些原因引起输入信号或压控振荡器频率发生变化,环路可以通过自身的反馈迅速进行调节。结果是VCO的输出频率、相位又被锁定在基准信号参数上,从而又维持了环路的锁定。这个过程人们称为环路的跟踪过程。系统能保持跟踪的最大频率范围或最大固有频带称为同步带或同步范围,或称锁定范围。

捕捉过程与跟踪过程是锁相环路的两种不同的自动调节过程。

由此可见,自动频率控制(AFC)电路,在锁定状态下,存在着固定频差。而锁相环路控制(PLL)电路,在锁定状态下,则存在着固定相位差。虽然锁相环存在着相位差,但它和基准信号之间不存在频差,即输出频率等于输入频率.这也表明,通过锁相环来进行频率控制,可以实现无误差的频率跟踪.其效果远远优于自动频率控制电路。

一.鉴相器(PD)

鉴相器是锁相环路中的一个关键单元电路,它负责将两路输入信号进行相位比较,将比较结果从输出端送出。 鉴相器的电路类型很多,最常用的有以下三种电路。

(1)模拟乘法器鉴相器,这种鉴相器常常用于鉴相器的两路输入信号均为正弦波的锁相环电路中。

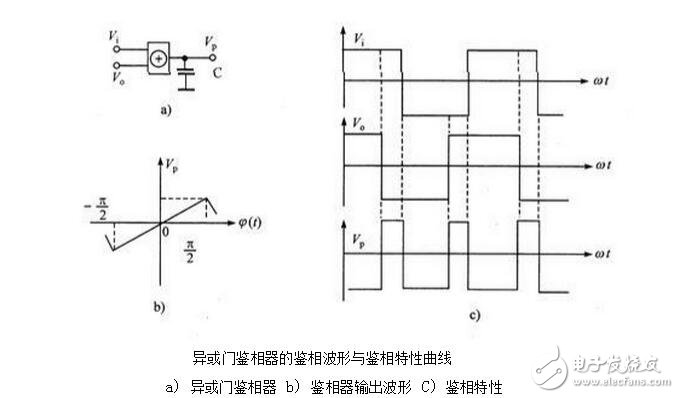

(2)异或门鉴相器,这种鉴相器适合两路输入信号均为方波信号的锁相环电路中,所以异或门鉴相器常常应用于数字电路锁相环路中。

(3)边沿触发型数字鉴相器,这种鉴相器也属于数字电路型鉴相器,对输入信号要求不严,可以是方波,也可以是矩形脉冲波,这种电路常用于高频数字锁相环路中。

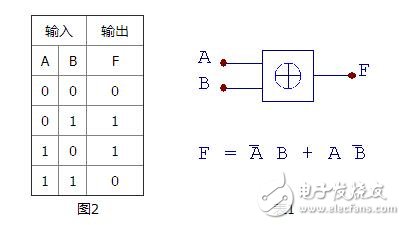

1.异或门鉴相器 异或门的逻辑真值表示于表1,图2是逻辑符号图。

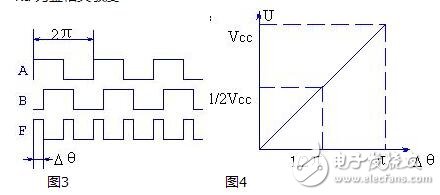

从表1可知,如果输入端A和B分别送入占空比为50%的信号波形, 则当两者存在相位差Dθ时,输出端F的波形的占空比与Δθ有关,见图3。将F输出波形通过积分器平滑,则积分器输出波形的平均值,它同样与Δθ有关,这样,我们就可以利用异或门来进行相位到电压的转换,构成相位检出电路。于是经积分器积分后的平均值(直流分量)为:

U = Vdd * Δ θ/π (1)

不同的Δθ,有不同的直流分量Vd。Δθ与V的关系可用图4来描述。从图中可知,两者呈简单线形关系:

Ud = Kd *Δθ (2)

Kd 为鉴相灵敏度

2.边沿触发鉴相器 前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。

二.压控振荡器(VCO)

压控振荡器是振荡频率ω0受控制电压UF(t)控制的振荡器,即是一种电压——频率变换器。VCO的特性可以用瞬时频率ω0(t)与控制电压UF(t)之间的关系曲线来表示。未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO的振荡频率,称为自由振荡频率ωom,或中心频率,在VCO线性控制范围内,其瞬时角频率可表示为:

ωo(t)= ωom + K0 UF(t)

式中,K0——VCO控制特性曲线的斜率,常称为VCO的控制灵敏度,或称压控灵敏度。

压控振荡器(VCO)是锁相环(PLL)的被控对象。压控振荡器是一个电压—频率变换装置,在环路中作为频率可调振荡器,其

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 锁相环在反馈电路上的应用(01-10)