低功耗同步解调器设计考虑因素

时间:07-25

来源:ADI

点击:

A2200输出噪声与频率无关,则预计有效位数将在输出数据速率每4×下降时增加一位。ENOB在较低输出数据速率下不会上升太多,这是由于ADA2200输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的主要成分。

线性度

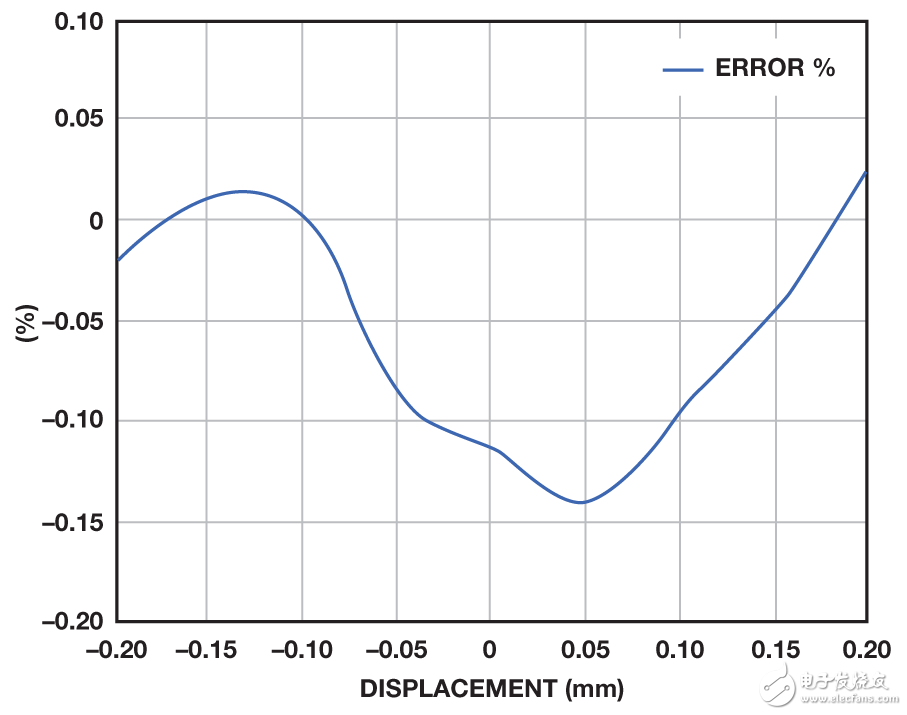

首先在±2.0 mm内核位移处执行一次两点校准即可测量线性度结果。由这些测量结果可确定斜率和失调,从而实现最佳直线拟合。然后,在±2.5 mm满量程范围内测量内核位移。从直线数据中减去测量数据即可确定线性度误差。

图7. 位置线性度误差与LVDT内核位移的关系

用于电路评估的E系列LVDT线性度额定值为±0.5%(±2.5 mm位移范围)电路性能超过了LVDT的规格。

功耗

电路总功耗为10.2 mW,包括驱动LVDT的6.6 mW以及电路其余部分的3.6 mW。电路SNR可以通过增加LVDT激励信号而得到改善,但代价是功耗更高。或者,可以通过降低LVDT激励信号从而降低功耗,同时使用低功耗双通道运算放大器来放大LVDT输出信号,以便保留电路的SNR性能。

结论

同步解调可以解决很多传感器信号调理所共有的特性挑战。低于1 MHz激励频率且动态范围要求为80 dB至100 dB的系统可以采用低成本、低功耗模拟电路;该方法所需的数字后处理极少。了解相敏检波器的工作原理以及传感器输出端的噪声特性是确定系统滤波器要求的关键。

- 经典案例分享,告诉你低成本、低功耗的同步解调器设计没那么难(07-21)

- RS-485网络设计降低功耗问题(01-26)

- 低功耗CMOS电压基准源的设计(08-27)

- 一种新型低功耗两级运算放大器的实现(01-20)

- 创建理想的低功耗设计(01-14)

- 新一代电池供电装置的超低功耗设计(07-18)