基于集成化的二阶滤波器UAF42设计50Hz陷波器

UAF42是一个集成化的二阶滤波器,可以用来设计复杂的滤波器。本文介绍了如何基于UAF42设计一个高性能的50Hz陷波器,并使用免费的仿真软件TINA对这个电路进行了仿真分析,供工程师参考和学习。

设计

众所周知,在滤波器设计时,运放的精度和温度稳定性是关键。UAF42里面集成了两片0.5%精度的1000pF的电容。

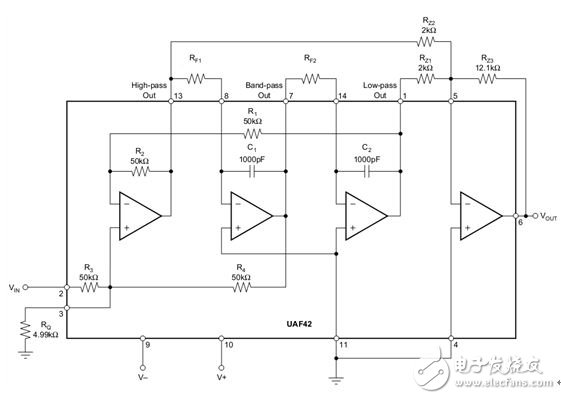

在工业应用中,多种场合需要用到50Hz陷波器。本节将介绍使用UAF42设计一个高性能的50Hz陷波器。使用UAF42来设计50Hz陷波器,只需要外加6个电阻即可组成一个50Hz陷波器。如下图所示

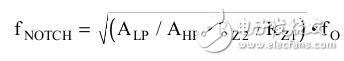

UAF42的辅助运放将高通和低通滤波器的输出相加,即得到陷波器。陷波器的陷波频率由下面的公式所决定,其中Alp为低通滤波器的增益,Ahp是高通滤波器的增益。

一般而言,ALP/AHP ? RZ2/RZ1=1。因此陷波器的中心频率即为:

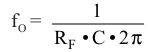

其中fo由下式确定:

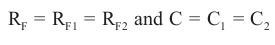

其中

参考UAF42的数据手册,C=1000pF,则RF=3.1831MΩ。

因此陷波器的中心频率可以由电阻Rf来确定。或都增加电容来确定。电容一般选求NPO电容,或云母电容,或其它低漏电高温度稳定性的瓷片电容。

关于电路的-3dB带宽则由下式来确定

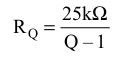

关于-3dB带宽的定义:BW-dB=fH-fL。上式中的Q由辅助运放的增益所决定。进而由Rq的值来设定,如下式:

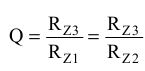

陷波器的通频带主要受滤波器Q参数的影响。Q参数由辅助放大电路的输入电阻和增益电阻所决定,如下式:

这里需要注意一点,基于UAF42的陷波器电路的陷波中心频fo和滤波器Q参数可以分别设置。

仿真

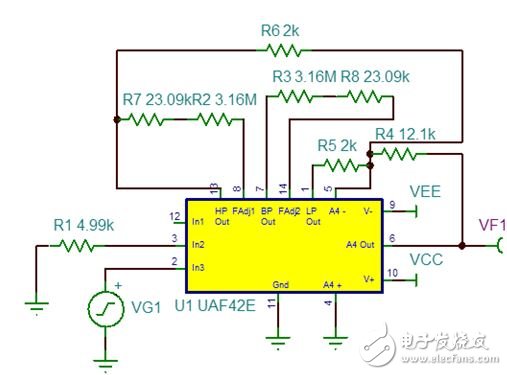

上一小节,我们设计出一个基于UAF42的50Hz陷波器。在本小节,我们将使用免费的仿真软件TINA对这个电路进行仿真分析。具体原理图如下所示。

其中3.1831M欧的电阻用两个E96标准的电阻串联组成。一个是3.16M欧,另一个为23.09K欧。选用E96标准电阻的主要原因是可以达到1%的精度要求,阻值容易搭配,成本较低。UAF42的电源选用+/-15V供电。

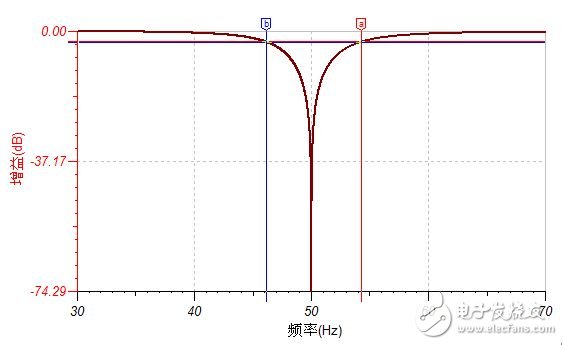

下面对设计的电路进行仿真,下图是设计的陷波器电路的仿真结果。可以看出在50Hz处有约-74dB的衰减。使用软件测量工具计算得其-3dB带宽为8Hz。

上图仅为仿真结果,受到器件精度及实际电路分布参数的影响,此陷波器的性能可能会略有下降。感兴趣的工程师可以制作PCB,实测一下。

陷波器 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)