工程师,为什么要关注JESD204?

时间:07-07

来源:电子发烧友网

点击:

为JESD204正名

当我们使用一个转换器的时候,我们很有必要了解采样信号及其数字表示之间的时序关系。这样做就可以在接收到信号的时候在模拟区域对采样信号进行适当的重建。会出现这种情况很明显就是在进行模数转换的时候,但在数模转换的时候同样适合。这个时序关系受到定义的ADC转换器输入信号瞬时采样边缘和转换器输出数字显示之间多个时钟周期的延迟影响。同样地,在DAC,延迟定义为数字信号转换成DAC直到模拟信号输出改变的这段时间内的时钟周期的数量。在JESD204和JESD204A的标准里,没有给准确设置转换器延迟和他的串行数字输入和输出定义的功能。

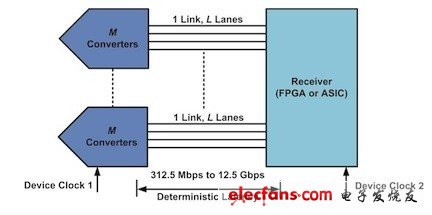

除此之外,转换器将会继续增加其速度和精度。这些要素就引出了这个标准第二个版本JESD204B的介绍。在2011年7月,第二个版本也就是现行本本的标准JESD204B推出,这个标准改进的一个管管元器件就是添加了规定去获得确定延迟,除此之外,数据速率支持逼近12.5Gbps,这就将设备分解成不同的速度等级。这个版本标准需要从用帧时钟作为时钟源到用设备作为主时钟源过渡。图3表示出了添加到JESD204B版本标准中的附加功能。

在JESD204标准的前两个版本里,没有严格规定通过接口的确定延迟。JESD204B版本通过提供一个机制、从电压升高周期到电压升高周期和通过链接再同步化,这样的话延迟就可以再重复和具有确定性。一个行之有效的方法就是通过初始化转换器初始通道的转换器排列顺序,同时及时利用一个叫做SYNC的输入信号对所有通道进行一个

JESD204 编辑视点 LVDS 转换器接口 DAC 相关文章:

- ADI公司的JESD204A数据转换器可减少功耗及电路板空间(07-03)

- 电磁兼容EMC预测试与鉴定测试(09-25)

- 电磁辐射的污染及治理的紧迫性(03-18)

- EMC常见缩略语清单(03-19)

- EMC(电磁兼容性标准)认证流程图(02-11)

- 微波暗室一般技术指标(09-25)