FPGA引脚信号如何分配?FPGA引脚分配的几个基本原则

分配FPGA引脚的几个原则

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

这里有一个前提,即假定设计师已经根据设计的大概规模和信号要求确定了目标器件范围和型号。对以下每一步都应在考虑单极信号前优先考虑差分对信号。

最先指配那些只能在特定引脚上工作的特殊信号,正常情况下是指串行I/O信号和全局时钟信号。其次指配大型和/或高速信号总线,特别是那些要跨越多个库或区域的信号。如果总线需要局部时钟,那么就要考虑具有更多局部时钟引脚的库或区域,并先指配局部时钟。

如果针对FPGA器件采用了多种I/O标准,那么设计师还必须先考虑将I/O信号映射到库/区。这一步需要慎重考虑,因为许多I/O标准和参考电压是不兼容的。一些I/O标准要求在特殊引脚上输入参考电压,使得这些引脚不可再用于一般用途。将高速输出和双向信号分开指配在一定程度上可避免同时开关输出噪声(SSO)问题。

第三,采用第二步中相同的基本规则指配速度较慢和约束较少的总线,但不用太多考虑SSO等问题。第四,最后完成个别信号的指配。如果只剩下少量引脚,或在第一次反复时用完了所有的引脚,可以考虑选用具有更多I/O数量的下一种器件,因为根据市场情况肯定还会临时增加某些功能,而且没有哪个设计师愿意在设计的最后阶段再做一遍指配过程吧。

在以上每一步中,要建立含有正确信号分配和I/O标准的约束文件,以及含有I/O设计部分的HDL文件。然后再开始布局和布线,因为按从最多约束信号到最少约束信号的顺序可以更好地发现错误

在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。

如何分配FPGA引脚信号

综合起来主要考虑以下的几个方面:

1、 FPGA 所承载逻辑的信号流向。

IC 验证中所选用的 FPGA 一般逻辑容量都非常大,外部的管脚数量也相当的丰富,这个时候就必须考虑到PCB 设计时的布线的难度,如果管脚的分配不合理,那么有可能在PCB 设计时出现大量的交叉的信号线,这给布线带来很大的困难,甚至走不通,或者是即便是布线走通了,也有可能由于外部的延时过大而不满足时序方面的要求。所以在管脚分配前对 FPGA 工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的 BANK 中

2、 掌握 FPGA 内部 BANK 的分配的情况。

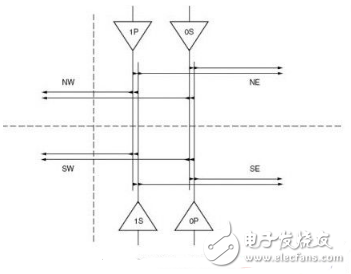

现在 FPGA 内部都分成几个区域,每个区域中可用的 I/O 管脚数量各不相同。在 IC 验证中都是采用了ALTERA 与 XILINX系列的 FPGA ,这两个厂商的 FPGA中内部BANK的分配有一定的差异,这可以在设计中查阅相关的手册。下面与 ALTERA 中 StraTIx II系列的 FPGA 内部 BANK 的分配为例来进行说明。

图中详细说明了 FPGA 内部 BANK 的分配情况和每个 BANK 中所支持的 I/O 标准。根据 FPGA 中内部BANK 的分配的情况,同时结合图 1 中信号的流向也就可以大体固定

FPGA 在单板中的方向,同时按照就近的原则将相关的信号分配到相关的 BANK 中,这样的方法可以完成一般信号的分配。

3、 掌握所选 FPGA 每个 BANK 所支持的 I/O 标准。

可以看出 FPGA 内部的每个 BANK 所支持的 I/O 的标准不尽相同,所以管脚的分配时要将支持相同标准的管脚都集中到一个 BANK 中,因为 FPGA 中同一个BANK一般不同时支持两种 I/O 标准,当然也有例外,这就需要查阅相关 I/O 标准所要求的工作条件。

4、 关注特殊信号的管脚的分配

这里的特殊信号主要是指时钟信号与复位信号,或者是一些要求驱动能力较高的信号。时钟信号一般都是要求分配到全局的时钟管脚,这样获得的时间的延迟将是最小的,驱动也最强。复位信号因为要求同步性好驱动的能力强,所以一般的情况下也会从全局的时钟管脚送入。在分配时钟时,根据时钟的多少

fpga 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)