综合详细分析电磁兼容分层

【前言】按照产品在电磁兼容设计时所采取的各项措施的重要性为先后,分为若干层次进行设计,并加以综合分析进行适当调整直到完善,这就是本文提出的" 电磁兼容分层与综合设计法"。可以做到电磁兼容试验一次成功。

人们在研发新产品时,往往急于实现产品的功能,于是沿用低频、低速时的经验,满足于利用软件将单片机、芯片和元器件连接起来,就希望实现产品功能、效能和性能,结果事与愿违,不仅只是在低水平徘徊,而且延误了宝贵的时间。

其实,随着集成电路时钟速率的提高,上升、下降沿速率加快,电源电压降低以及产品复杂性和密集度的提高、设计周期的不断缩短,沿用低频、低速时的经验已完全不能实现产品的功能、效能和性能。如果在产品设计的后期重新设计,则成本很高。如果延误日期,损失就更大。

因此,"第一时间推出产品"的设计目标,是生死攸关的竞争需要。要在第一时间实现产品规定功能、使产品效能得以充分发挥,并达到最高性能,就必须做好EMC设计。为了以最低的成本解决EMC问题,就必须在功能设计的同时,进行EMC设计,并选用正确的方法。

现在,产品设计的重点已从功能设计和逻辑设计,转移到EMC设计上来了。

进行电磁兼容设计的正确方法,应做到:标本兼治,重在治本。 就是从治理电磁兼容问题的源头出发,按重要性为先后,分为若干层次进行设计,并加以综合分析,进行适当调整,直到完善:

第一层为重在治本之一:有源器件的选型和印刷电路板设计

第二层为重在治本之二:接地设计

第三层为标本兼治之一:结构/屏蔽设计

第四层为标本兼治之二:滤波设计

第五层为标本兼治之三:瞬态骚扰抑制设计

第六层为系统级电磁兼容设计

并且在每一层进行接地、屏蔽和滤波的综合设计和软件抗骚扰设计。这就称为"电磁兼容分层与综合设计法"。可以做到电磁兼容试验一次成功。

"电磁兼容分层与综合设计法" 是本文作者在2000年5月"全国电磁兼容标准与质量认证研讨会"上,首次提出,至今已十余年。在全国推广十余年以来, 一批企业先后走出"测试修改法"导致电磁兼容试验失败的"怪圈",做到在产品设计之初,就主动进行电磁兼容设计。而且,电磁兼容设计的投入仅需1% (国内一般为5%至10%)。既降低了成本,又缩短了研发时间。同时,也使"电磁兼容分层与综合设计法"更加充实与完善,得到了全国许多企业和单位的认可。

第一层 有源器件的选型和印刷电路板设计

在电磁兼容问题的源头,根本上解决EMC问题,必须首先做好芯片的选型和印刷电路板设计。

一.有源器件的敏感度特性与发射特性

1. 电磁敏感度特性

模拟器件带内敏感度特性取决于灵敏度和带宽;带外敏感度特性用带外抑制特性表示。

逻辑器件带内敏感度特性取决于噪声容限或噪声抗扰度,带外敏感度特性也是用带外抑制特性表示。

2.电磁发射特性

逻辑器件是一种骚扰发射较强的最常见的宽带骚扰源。时钟波形的上升时间tr 越短,对应逻辑脉冲所占带宽越宽

BW=1/ptr

此带宽也是最高频率分量。实际辐射频率范围可能达到BW的十倍以上。通过器件手册可以查出tr的典型值。

人们普遍认为:在PCB设计中,需要考虑的关键问题是时钟频率,其实,时钟波形的上升时间tr才是最关键的因素。上升时间tr定义为从波形的10%处上升到90%处所需要的时间。如果在互连线的一端输入方波,要求在另一端也得到方波,则该互连线不仅必须能传输方波的基波,还必须能传输全部高次谐波,至少为15次谐波。这就是说,PCB的时钟频率并不重要,上升时间tr和需要重新产生的谐波才是最重要的。描述这个要求的词语就是带宽BW,也即最高频率分量。

3. △I 噪声电流、瞬态负载电流IL的产生和危害

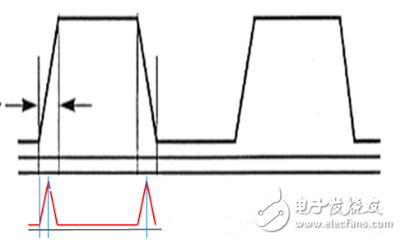

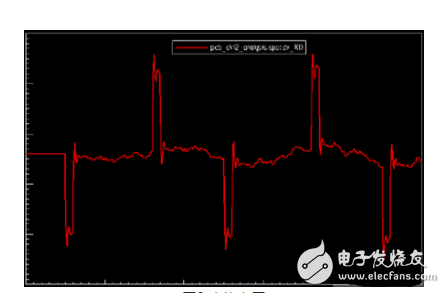

当数字集成电路在加电工作时,它内部的门电路将会发生 "0"和"1"的变换,即开关状态。在变换的过程中,该门电路中的晶体管将发生导通和截止状态的转换,会有瞬间变化电流-浪涌电流di/dt从所接电源流入门电路,或从门电路流入地线,这个变化电流就是△I噪声的初始源,称△I噪声电流。如图1所示。

图1 △I噪声电流

设驱动线对地电容与驱动门输入电容之和为负载电容 Cs,平时被充电,其值为电源电压。驱动门由高电位翻转为低电位时Cs放电,放电电流称为瞬态负载电流:

IL = Cs&TImes;dv/dt

瞬态负载电流IL与△I噪声电流复合后,会产生更强的电磁骚扰发射。是阻碍实现产品规定功能、使产品效能得不到充分发挥的主要原因。由于PCB上,信号线、电源线和地线等都存在一定的引线电感L,瞬态负载

- 高速DSP系统的电路板级电磁兼容性设计(10-23)

- 开关电源技术发展历程的十个关注点(08-28)

- 单片机系统的电磁兼容性设计详细解析(03-24)

- 关于单片机系统的电磁兼容性设计的几大误区(03-27)

- 单片机在电源设计中的应用(06-07)

- 基于单片机的锅炉液位控制装置设计(07-22)