综合详细分析电磁兼容分层

电流IL与△I噪声电流复合后产生的瞬间变化电流di/dt,将通过引线电感L的感抗引起尖峰电压

V= - Ldi/dt

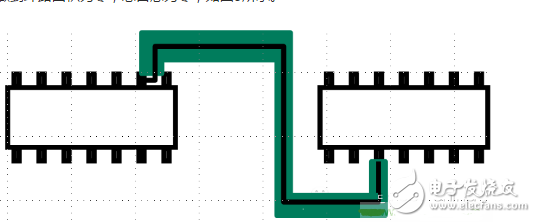

即△I噪声电压,称为同步开关噪声(Simultaneous Switch Noise SSN),如图2所示,会引发地电位和电源电压的波动(Ground/Power Bounce),产生电磁骚扰发射。所以,引线电感L是产生传导骚扰和辐射骚扰的根源之一。

图2 尖峰电压

电磁骚扰发射的另一根源为等效电压源的源阻抗,也即电源分配系统输入阻抗Z,系统要求尖峰电压应在正常电源电压的±2.5%至±5%以内。等效于源阻抗Z要足够低

V= Z&TImes;ΔI

不论ΔI如何变化,都可保持V变化很小。这可通过安装去耦电容达到。

理想电源的源阻抗Z为零,电源平面上任何一点电位保持恒定。

4.掌握IC设计和封装特性抑制EMI

IC封装也是产生电磁骚扰的原因之一。 IC封装包括芯片,内部PCB以及焊盘。直接影响IC封装的电容和电感。

芯片是作为系统的一部分而存在的,硅芯片必须采用某种封装,然后焊接到PCB板上。 这一互连链,即芯片通过封装连接到PCB板上,本身就是一个复杂系统。

应将芯片设计、封装和印刷电路板作为一个系统来考虑。以保证最后组装和加电后能得到所期望的结果。最好的方法是,对所有这些进行并行设计、分析和验证。

封装是指安装半导体集成电路芯片用的外壳,它不仅起着安放,固定,密封,保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁--芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印制板上的导线与其它器件建立连接。衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好,引线电感越小。封装技术已经历了好几代的变迁:

1)通孔插入式封装(Through-hole Package)

DIP(Dual In-line Package) 双列直插式封装:上世纪 70年代的封装,最大引脚数64条。其芯片面积/封装面积为1:8.6,离1相差很远,说明封装效率很低,引线很长,引线电感很大;

PGA(Pin Grid Array)针栅阵列式封装,引脚中心距为2.54mm,引脚数为64-447。表面安装式PGA引脚中心距为1.27mm,引脚数为250-528,引线电感很大;

2)表面安装式封装(Surface Mounted Package )

上世纪80年代出现了芯片载体封装,有陶瓷无引线芯片载体封装LCCC,塑料有引线芯片载体封装PLCC,小尺寸封装SOP(Small Outline Package),塑料四边引出扁平封装PQFP。芯片面积/封装面积为1:7.8,引线电感仍很大;

3)BGA封装与CSP封装

上世纪90年代随着集成技术的进步和深亚微米技术的使用,LSI,VLSI,ULSI相继出现,芯片集成度不断提高,对封装要求更加严格,I/O引脚数急剧增加,功耗也随之增大。为满足发展的需要,在原有封装品种基础上,又增添了新的品种--球栅阵列封装简称BGA(Ball Grid Array Package)。成为CPU南北桥等VLSI芯片的高密度,高性能,多功能及高I/O引脚封装的最佳选择。芯片面积/封装面积为1:4,引线电感有所减小;1994年9月诞生了一种新的封装形式命名为芯片尺封装,CSP(Chip Size Package或ChipScale Package),芯片面积/封装面积为1:1.1。也就是说,单个芯片有多大,封装尺寸就有多大,引线电感大大减小;

4)裸芯片组装

随着组装密度和IC的集成度的不断提高,为适应这种趋势,IC的裸芯片组装形式应运而生,并得到广泛应用。它是从已完工的晶圆(Water)上切下的芯片,不按传统之 IC 先行封装成体,而将芯片直接组装在电路板上,谓之 Bare Chip Assembly。早期的 COB (Chip on Board)做法就是裸芯片的具体使用,不过 COB 是将芯片的背面黏贴在板子上,再行引线及胶封。而新一代的 Bare Chip 却连引线也省掉,是以芯片正面的各电极点,直接反扣熔焊在板面各配合点上( Flip Chip)。或以芯片的凸块扣接在载带自动键合(TAB)的内脚上,再以其外脚连接在 PCB 上。此二种新式组装法皆称为 裸芯片组装,寄生 C,L小。并且可节省整体成本约 30% 左右;

5)载带自动键合(TAB):多接脚大型芯片组装:裸芯片贴装技术之一

载带基材为聚酰亚胺薄膜,表面覆盖上铜箔后,用化学法腐蚀出精细的引线图形。芯片在引出点上镀Au、Cu或Sn/Pn合金,形成高度为20-30mm的凸点电极。组装方法是将芯片粘贴在载带上,将凸点电极与载带的引线连接,然后用树脂封装。它适用于大批量自动化生产。TAB的引线间距可较QFP进一步缩小至0.2mm或更短。

6)系统芯片(SoC)

SoC就是将系统的全部功能模块集成到单一半导体

- 高速DSP系统的电路板级电磁兼容性设计(10-23)

- 开关电源技术发展历程的十个关注点(08-28)

- 单片机系统的电磁兼容性设计详细解析(03-24)

- 关于单片机系统的电磁兼容性设计的几大误区(03-27)

- 单片机在电源设计中的应用(06-07)

- 基于单片机的锅炉液位控制装置设计(07-22)