基于Vivado HLS的Down Scaler视频系统设计

3 视频系统设计

3.1 系统参数要求

输入视频流为全高清视频、1920x1080P/60fps、YUV4:4:4 格式,输出视频流为高清视频、1080x720P/60fps、YUV4:4:4格式,要求Down Scaler模块的工作频率等于输入视频像素频率,即 148.5MHz。

3.2 Down Scaler视频系统搭建

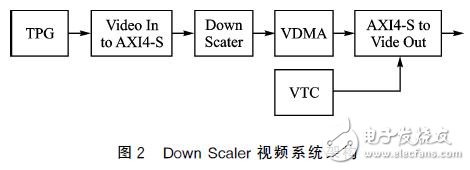

实时视频系统架构可以分为两大类,一类是不含帧缓存模块的系统,另一类是包含帧缓存模块的系统,本文中的Down Scaler视频系统属于第二类架构。

根据图2所示的系统架构,使用 IP integrator 搭建的Down Scaler视频系统,该系统用到以下IP核:

①Test Pattern Generator [3]——Xilinx IP核,用来产生不同格式的输入视频流;

② Down Scaler——Vivado HLS生成的IP核

③ AXI Video Direct Memory Access [4]、AXI Interconnect [5]、MIG 7Series [6]——Xilinx IP核用来在DDR内存中构建帧缓存器;

④ Clocking Wizard [7] Xilinx IP核,用来生成系统时钟信号;

⑤ Proc Sys Reset——Xilinx IP核,用来生成系统重置信号;

⑥ Video In to AXI4-S [8]、AXI4-S to Video Out [9]———Xilinx IP核,用来进行 AXI4-Stream和视频协议转换;

⑦ VTC (Video TIming Coneroller [10]——Xilinx IP核,用来检测输入视频时钟周期和产生输出视频时钟周期。

至此,一个基于Vivado HLS的Down Scaler视频系统设计完成。

结 语

本设计选取Xilinx Kintex-7评估板作为开发平台,使用高层次综合工具Vivado HLS进行Down Scaler模块的设计、仿真和验证,使用Vivado进行实时视频系统构建,在满足实时性要求和FPGA资源消耗要求下,实现了对Down Scaler视频算法从PC端软件处理向FPGA平台硬件处理的移植。经测试,由TPG生成的1080P视频流经过本文设计的Down Scaler系统,成功输出了720P视频流,Down Scaler的性能满足了设计要求。

随着系统设计和算法日益复杂,新的设计方法———高层次综合开始出现并将逐渐取代传统的硬件系统设计方法,成为系统设计的主流方式。未来的设计者可以从算法的角度直接下降到硬件平台来完成硬件开发,对于复杂的算法,这一方法将大幅缩短开发周期,显著降低代码量,同时也为算法工程师和软件工程师打开了硬件设计的大门。

- Scaler IP仿真时,所有的输出数据都是0是怎么回事?(02-27)

- 如何利用Vivado HLS处理许多位准确或任意精度数据类型(02-07)

- Vivado环境下如何在IP Integrator中正确使用HLS IP(02-07)

- C++中常用的复合数据类型在Vivado Hls中的应用方法(02-07)

- 使用Vivado HLS创建一个EDK PCore(02-09)

- Zynq交叉编译环境链的建立与C程序编写(02-10)