C++中常用的复合数据类型在Vivado Hls中的应用方法

在C++中常用的复合数据类型,一种是结构体,另一种就是枚举类型。

struct

对于struct来说,如果出现在顶层函数,并作为顶层函数参数的时候,struct里的scalar变量就会被映射scalar类型的端口,数组就会被映射为相应的memory端口。在实际使用中,建议预先把结构体在头文件里声明。对于结构体中的元素,Vivado hls里提供相应的data pack优化方式,这种优化方式分为两种,即field_level 和struct_level。

两者区别

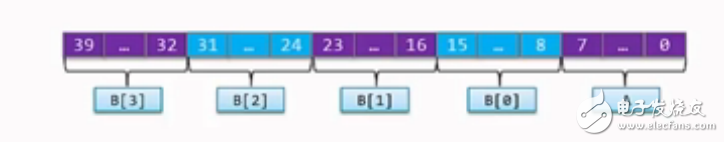

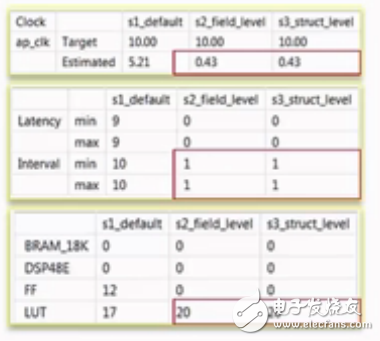

结构体里field_level所有元素的位宽必须以8 bits为边界,比如说,一个变量为6 bits就必须扩展到8 bits,如果一个struct有五个元素,每个元素6 bits,每个元素扩展到8 bits,此时总位宽就会被扩展为40 bits。而struct_level不改变每个元素的实际位宽,但是对于封装后的总位宽要以8 bits为边界,比如说,上面的·总位宽就会被扩展到32 bits。

注意:比较这两种类型的data pack优化方式,会发现两者的clock,latency和interval,以及资源利用率都是一致的。data pack可以降低latency和interval,提高数据的吞吐率,这是因为这里data pack对for循环进行展开。

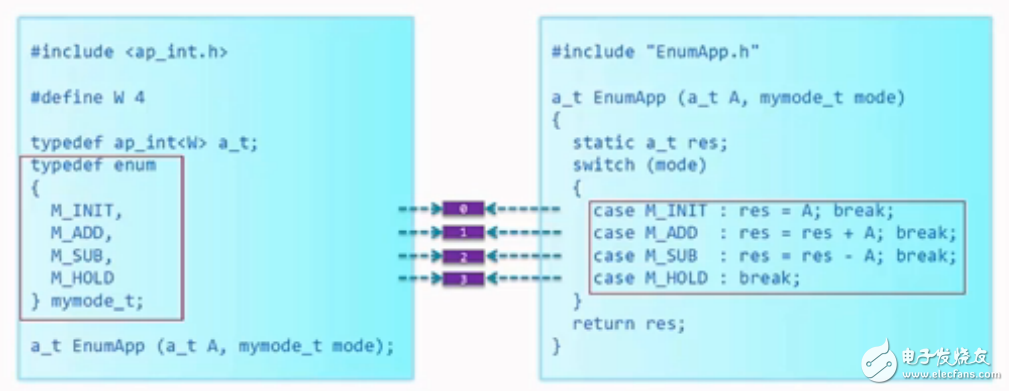

Enum

Enumerated Type是将一个数值定义为一个符号常量,需要用到关键字enum。枚举类型的元素会被自动的分配到一个整数,其中起始值为0,后面依次加1。这样是为了提高代码的可读性。

总结

Vivado hls既支持结构体,也支持枚举类型,这两种类型都可以作为接口出现在顶层函数。如果结构体出现在顶层函数,可以通过field_level 和struct_level进行封装,如果枚举类型作为接口出现在顶层函数,它实际上是整数,vivado会自动推断相应mode的数据位宽。

- 强化DPD演算效能 SoC FPGA提升蜂巢网络设备整合度(08-16)

- Vivado环境下如何在IP Integrator中正确使用HLS IP(02-07)

- 使用教程分享:在Zynq AP SoC设计中高效使用HLS IP(一)(02-07)

- 使用教程分享连载:在Zynq AP SoC设计中高效使用HLS IP(二)(02-07)

- 使用Vivado HLS创建一个EDK PCore(02-09)

- FPGA专家教您如何在FPGA设计中使用HLS(02-10)