Vivado环境下如何在IP Integrator中正确使用HLS IP

概叙

通常来说,我们不仅要用高级综合package RTL,还可以利用内部IP Integrator。本文是一个复杂的FFT数据块的设计,介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中使用他们,最终使用RTL testbench来验证设计。

Integrate带有Xilinx IP Block的 HLS IP

这里展示了在IP Integrator中,如何将两个HLS IP blocks跟Xilinx IP FFT结合在一起 ,并且在Vivado中验证设计。

Step 1: 创建 Vivado HLS IP Blocks

使用提供TCL脚本的Vivado IP,创建两个HLS block。脚本给这两个HLS设计运行HLS C综合,RTL co-simulaTIon和package IP。

脚本完成后,会生成两个Vivado HLS project(fe_vhls_prj和be_vhls_prj),它们都包含Vivado IP。下面展示Vivado HLS IP blocks如何在IP Integrator中集成到设计,并且验证IP。

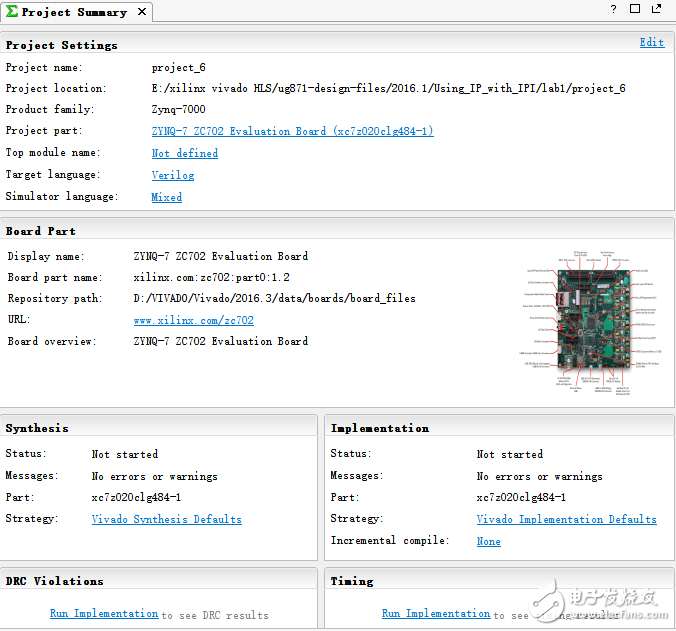

Step 2: Create a Vivado Design Suite Project

打开Vivado,创建New Project,在project setTIng选择:E:\xilinx vivado HLS\ug871-design-files\2016.1\Using_IP_with_IPI\lab1,然后选择RTL Project和 Do not specify sources at this TIme,最后在Board里选择ZYNQ-7 ZC702,点击finish

Step 3: Add HLS IP to an IP Repository

先后点击IP Catalog和IP SetTIngs,在弹出的Project Settings窗口里,选择Repository Manager下面的Add Repository,分别添加lab1/hls_designs/fe_vhls_prj/IPXACTExport/impl/ip/ 和 lab1/hls_designs/be_vhls_prj/IPXACTExport/impl/ip/

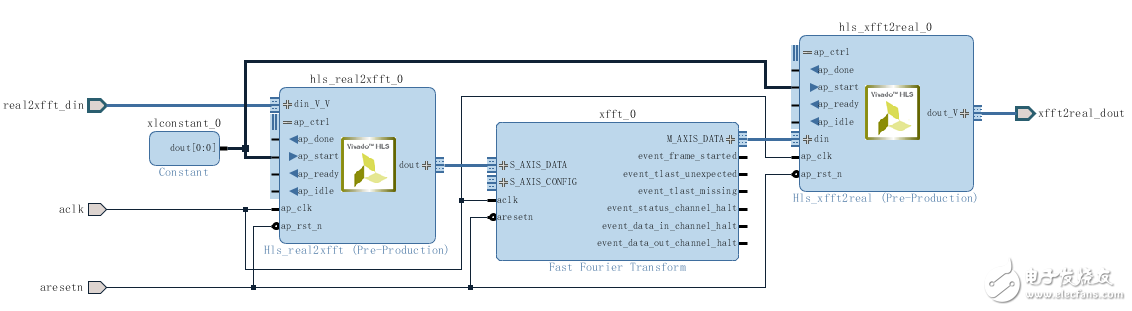

Step 4: Create a Block Design for RealFFT

1.点击Create Block Design,并将Design name命名为RealFFT,选择Add IP,在搜索里输入Fast Fourier Transform

2.双击Fast Fourier Transform IP去打开Re-customize IP,设置Transform Length为512,并选择在Architecture Choice里选择Pipelined, Streaming I/O

3.在Implementation窗口里,将Control Signals设置ARESETN,在Throttle Scheme设置为Non Real Time

4.Add IP,搜索hls,将搜索到的两个IP添加进设计,然后连接HLS和FFT block的端口(连接如下),然后给hls_real2xfft的din_V_V 接口和Hls_xfft2real的dout_V 接口 选择Make External,添加外部接口并分别命名为eal2xfft_din和xfft2real_dout,同理给FFT的aclk和aresetn端口分别Make External,添加 constant IP,联线如下,最后点击Regenerate Layout

5.点击Validate Design,这时会出现一些 warnings,它们是跟FFT的 s_axis_config pin相关。

注意:这里xff的t配置接口悬空,这是因为由于本设计始终运行在默认模式,现在点击OK 关闭messages,然后点击File > Save Block Design。

6.在Sources窗口右击RealFFT.bd,并选择 generate output products,然后在Sources窗口给RealFFT.bd创建HDL Wrapper。

Step 5: Verify the Design

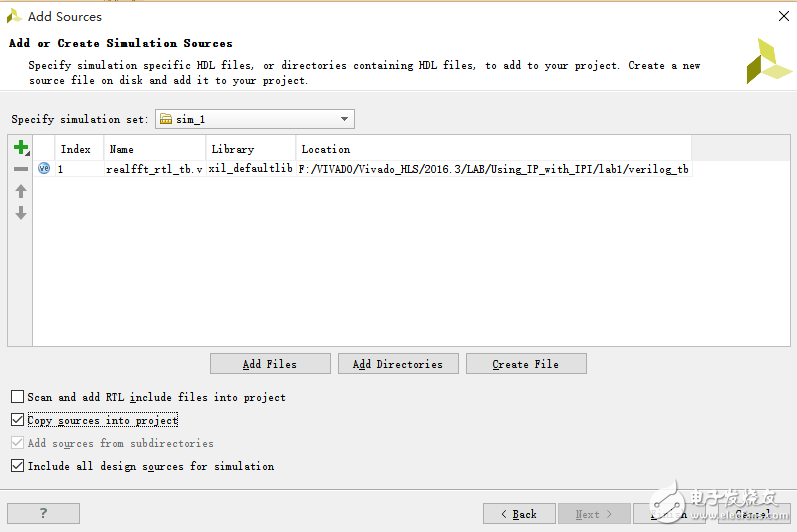

下面就是用realfft_rtl_tb.v验证设计

1.右击Sources窗口里的Simulation Sources,选择Add Sources,在弹出的窗口里选择Add or Create Simulation Sources,然后Add Files,选择Using_IP_with_IPI\lab1\verilog_tb文件夹,并选择Copy sources into the project

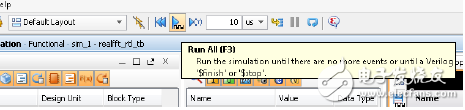

2.在Run Simulation里选择Run Behavioral Simulation,一旦simulation开始了,点击Run All就完成了simulation

总结

本文介绍了如何使用Tcl脚本创建Vivado HLS IP,如何使用IP integrator(IPI)导入创建好的设计,并且包括Xilinx IP和Vivado IP blocks,以及如何在IPI验证设计。

- 强化DPD演算效能 SoC FPGA提升蜂巢网络设备整合度(08-16)

- C++中常用的复合数据类型在Vivado Hls中的应用方法(02-07)

- 使用教程分享:在Zynq AP SoC设计中高效使用HLS IP(一)(02-07)

- 使用教程分享连载:在Zynq AP SoC设计中高效使用HLS IP(二)(02-07)

- 使用Vivado HLS创建一个EDK PCore(02-09)

- FPGA专家教您如何在FPGA设计中使用HLS(02-10)