基于Vivado HLS的Down Scaler视频系统设计

摘要:介绍一种基于FPGA的 Down Scaler视频系统设计。系统的核心部件采用Xilinx Kintex-7的板载XC7K325T 芯片,系统设计使用Vivado工具,包括使用Vivado HLS进行Down Scaler模块设计。首先按照Vivado HLS的代码规范进行Down Scaler模块的C/C++代码编写,然后利用编译工具生成RTL级代码和综合结果Down Scaler IP核,最后将Down Scaler IP核与TPG、VDMA等Xilinx视频IP核互连,构建实时视频系统。在满足实时性要求和FPGA资源消耗要求的条件下,该设计实现了对Down Scaler视频算法从PC端软件处理方式向FPGA平台硬件处理方式的移植。

引言

在电子设计自动化领域,高层次综合工具变得越来越受欢迎,其能够将C/C++、SystemC 、Matlab等高级语言的函数转译成RTL级的代码,这一功能将数字电路设计的抽象层进一步提升。随着嵌入式系统复杂程度的增加,高层次综合工具开始深入电子系统尤其是嵌入式系统的设计流程。本文介绍一种基于Xilinx公司的高层次综合工具Vivado HLS的Down Scaler视频系统设计。

1高层次综合概述

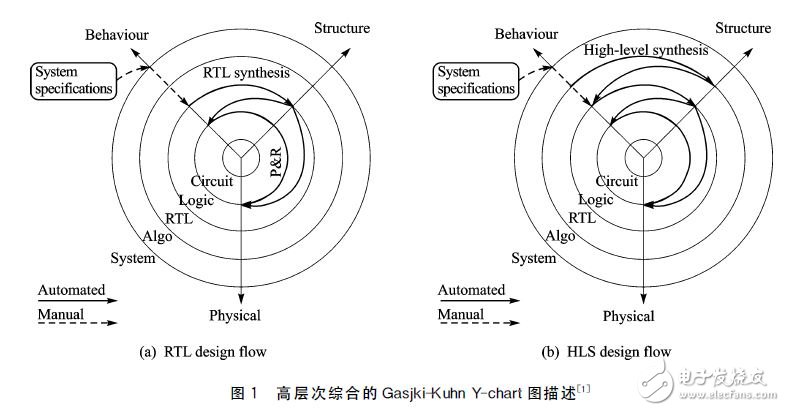

在过去20年,占主导地位的电子设计流程中,硬件设计人员需要手工完成从系统功能指标到RTL级代码的所有工作。如今,这样的设计流程开始变得困难,因为越来越多的功能可以被集成在一个芯片上,按照传统的设计流程,开发人员独自一人完成所有的功能变得越发困难,但因为设计功能的增多而增加设计团队的人员数量,从经济角度上看是不可行的,这意味着设计生产率必须有所提高。高层次综合能够通过从算法层到RTL层的自动化来提高设计生产率,从图1(b)中可以看到,应用高层次综合,系统设计从功能指标到自动化设计流程开端的距离缩短了。

在设计流程中,应用高层次综合工具能够给设计工作带来以下便利:首先,需要设计人员编写的代码量显著减少,在缩短开发周期的同时降低了错误率。其次,在如今的产品开发过程中,验证所需的时间往往超过设计的时间,使用高层次综合工具能够缩短验证时间,在高层次综合工具生成设计代码的同时,还能够同时生成测试平台代码,可以直接通过测试数据来验证设计代码是否正确。

2Down Scaler模块设计

传统的Down Scaler运算是在PC架构下进行的,以汤姆逊视频网络公司的产品 THVN VS7000为例,其中的 Down Scaler模块是PC服务器中的一个C++应用程序,在进行运算处理前,视频流的获取通过一块 Black Magic板卡来实现,其接收到的每一帧图像的像素信息通过PCIe传输到PC服务器。服务器首先将像素信息存储在3个不用的内存空间Y、U、V,之后应用程序Down Scaler对这3个空间的像素信息进行运算处理。本文描述的设计目标是使用FPGA中的一个Down Scaler IP核实现对视频流的"硬件处理",代替传统PC端的Down Scaler C++程序对图像进行"软件处理"的方案,从而取消完整帧像素信息Y、U、V成分的预储存步骤。

2.1 模块参数要求

视频的缩小比例为2/3,像素的相位数为2,根据相位数、亮度色度、水平竖直的不同情况,共计有8个滤波窗,每个滤波窗包含11个参数,由 Lanczos算法提前计算确定,"镜像"处理针对图像边缘的5个像素点进行。

2.2 模块设计关键点

2.2.1 计算单元

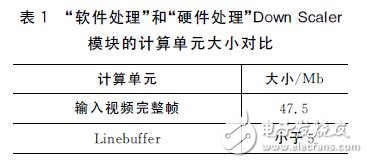

根据参数要求,Down Scaler模块包括两种BRAM计算单元,分别是Window和Linebuffer。 Window是一个一维存储空间,用来存储11个像素点,Linebuffer是一个二维存储空间,用来存储11行像素点。Linebuffer在每一个工作频率上接收新的输入像素,之前的像素在每一个工作频率上向存储空间的下方移动一个位置,即最新接收的像素点总是存储在Linebuffer中的初始位置。当Linebuffer填满后,Downscaling运算开始,即通过Window 存储11个采样像素,并对像素信息进行滤波运算。相比存储一帧完整图像后再进行运算的"软件处理"方式,通过使用Linebuffer和Window作为"硬件处理"方式的存储单元大幅降低了模块对存储空间的需求。"软件处理"和"硬件处理"Down Scaler模块的计算单元大小对比如表1所列。

2.2.2 像素信息计算和镜像运算整合

与传统Down Scaler算法对像素分量Y、U、V进行区分后再做镜像、滤波运算不同,本文中的Down Scaler对输入的像素点信息直接进行镜像和滤波运算,这样做是为了简化IP结构,更好地适应 AXI4-Stream协议[2]。另外,传统Down Scaler算法包含4个串行过程,分别是水平镜像、水平缩小、竖直镜像和竖直缩小,使用Vivado HLS工具的 Dataflow模式将串行过程并行执行后,在不改变模块工作频率的条件下,只能够满足对 1920x1080P/25fps的视频进行实时运算。为了进一步提高运算性能,需要进一步降低运算过程之间的数据依赖性。新的算法只包含两个缩小过程,即水平缩小和竖直缩小,镜像运算被整合在缩小运算中,并且只在需要的时刻进行。对镜像运算的整合虽然增加了算法编写的复杂程度,但是缩短了过程间的数据传输链路,使设计最终能够达到性能参数要求,满足对1920x1080P/60fps的视频进行实时运算。

- Scaler IP仿真时,所有的输出数据都是0是怎么回事?(02-27)

- 如何利用Vivado HLS处理许多位准确或任意精度数据类型(02-07)

- Vivado环境下如何在IP Integrator中正确使用HLS IP(02-07)

- C++中常用的复合数据类型在Vivado Hls中的应用方法(02-07)

- 使用Vivado HLS创建一个EDK PCore(02-09)

- Zynq交叉编译环境链的建立与C程序编写(02-10)