FPGA实战开发技巧(5)

其中[IN | OUT] 说明约束的是输入还是输出。"offset_time"为数据和有效时钟沿之间的时间差,{BEFORE| AFTER} 表明该时间差是在有效时钟之前还是之后,"clk_name"为有效时钟的名字,[TIMEGRP "group_name"] 是用户添加的分组信号,在缺省时,默认为时钟clk_name 所驱动的所有触发器。偏移约束通知布局布线器输入数据的到达时刻,从而可准确调整布局布线的过程,使约束信号建立时间满足要求。

1)"OFFSET IN"偏移约束

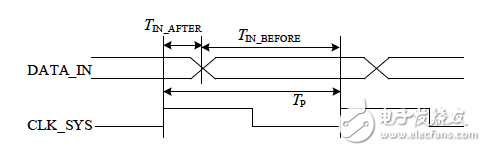

"OFFSET IN "偏移约束是输入偏移约束,有OFFSET_IN_AFTER 和OFFSET_IN_BEFORE 两种,前者定义了输入数据在有效时钟到达多长时间后可以到达芯片的输入管脚,这样可以得到芯片内部的延迟上限,从而对那些与输入引脚相连的组合逻辑进行约束;后者定义数据比相应的有效时钟沿提前多少时间到来,是与其相连的组合逻辑的最大延时,否则在时钟沿到来时,数据不稳定,会发生采样错误。输入偏移的时序关系如图5-10所示。

图5-10 输入偏移的时序关系

例如:

NET" DATA_IN" OFFSET = IN 10.0 BEFORE" CLK_50MHz";

表明在时钟信号CLK_50MHz 上升沿到达前的10ns 内,输入信号DATA_IN 必须到达数据输入管脚。

NET" DATA_IN" OFFSET = IN 10.0 AFTER" CLK_50MHz";

表明在时钟信号CLK_50MHz 上升沿到达后的10ns 内,输入信号DATA_IN 必须到达数据输入管脚。

2)"OFFSET OUT"偏移约束

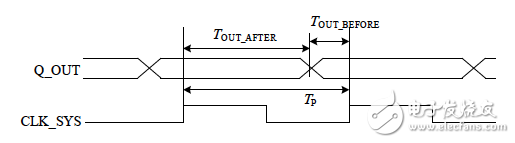

"OFFSET OUT"偏移约束是输出偏移约束,有OFFSET_OUT_AFTER 和OFFSET_OUT_BEFORE 两种,前者定义了输出数据在有效时钟沿之后多长时间稳定下来,是芯片内部输出延时的上限;后者定义了在下一个时钟信号到来之前多长时间必须输出数据,是下一级逻辑建立时间的上限。输出偏移的时序关系如图5.3.11 所示。

图5-11 输出偏移的时序关系

例如:

NET" DATA_OUT" OFFSET = OUT 10.0 BEFORE" CLK_50MHz";

表明在时钟信号CLK_50MHz 上升沿到达前的10ns 内,输出信号DATA_OUT 信号必须离开数据输出管脚。

NET" DATA_OUT" OFFSET = OUT 10.0 AFTER" CLK_50MHz";

表明在时钟信号CLK_50MHz 上升沿到达后的10ns 内,输出信号DATA_OUT 信号必须一直保持在数据输出管脚上。

3.分组约束

分组约束可有效管理大量的触发器、寄存器和存储器单元,将其分为不同的组,每组附加各自的约束,在大型设计中有着广泛的应用。

1)TNM/TNM_NET 约束

TNM/TNM_NET 约束用于选出可构成一个分组的元件,并对其重新命名,然后整体添加约束。除了IBUFG和BUFG 外,所有的FPGA 内部元件都可以用TNM 来命名,其语法规则为:

{NET|INST|PIN}" ob_name" TNM =" New_name";

其中"ob_name"为NET、INST 以及PIN 的名称,New_name 为分组的名称。例如:

INST ff1 TNM = MY_FF1;

NIST ff2 TNM = MY_FF1;

将实例ff1 与ff2 添加到新分组MY_FF1 中。

此外,TNM 语法也支持通配符"?"和"*",提高了在大规模设计中添加分组约束的效率。

当TNM 约束附加在线网上时,则该路径上所有的同步元件都会被添加到分组中,但不会穿过IBUFG 组件;

当TNM 约束附加到宏或原语的管脚上,则被该引脚驱动的所有同步元件会被添加到新分组中;当TNM 约束附加到原语或宏上,则将原语或宏添加到新的分组中。

TNM_NET 约束专门用来完成网线的分组,与TNM 不同的是,TNM 可以穿越IBUFG/BUFG。因此,如果把TNM 约束添加到端口上,则只能定义该端口;而要是把TNM_NET 添加到端口上,则可穿越BUFG,受该端口驱动的所有组件都将被添加到分组中。

2)TIMEGRP 约束

TIMEGRP 用于分组合并和拆分,将多个分组形成一个新的分组。其合并分组的语法为:

TIMEGRP" New_group" =" Old_group1" " Old_group2" … ;

其中,New_group 为新建的分组,而Old_group1 和Old_group2 以及…为要合并的已有分组。

拆分分组的语法为:

TIMEGRP" New_group" =" Old_group1" EXCEPT" Old_group2";

其中Old_group2 是Old_group1 的子集,New_group 为Old_group1 中除去Old_group2 之外所有的部分。

3)TPSYNC 约束

TPSYNC 用于将那些不是管脚和同步元件的组件定义成同步元件,以便可以利用任意点来作为时序规范的终点和起点。其相应的语法为:

{NET|INST|PIN}" ob_name" TPSYNC=" New_part";

将TPSYNC 约束附加在网线上,则该网线的驱动源为同步点;附加在同步元件的输出管脚上,则同步元件中驱动该管脚的源为同步点;附加在同步元件上,则输出管脚为同步点;附加在同步元件的输入管脚上,则

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)