大唐电信FPGA/CPLD数字电路设计经验分享(3)

工作频率。

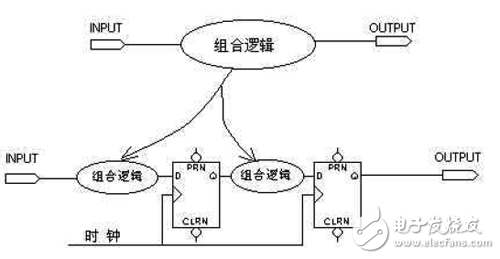

如图2所示:我们可以将较大的组合逻辑分解为较小的几块,中间插入触发器,这样可以提高电路的工作频率。这也是所谓"流水线"(pipelining)技术的基本原理。

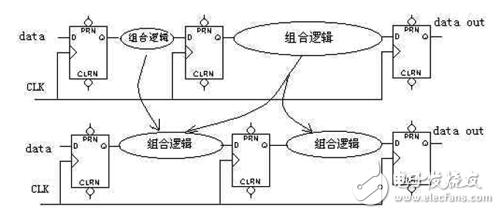

对于图3的上半部分,它时钟频率受制于第二个较大的组合逻辑的延时,通过适当的方法平均分配组合逻辑,可以避免在两个触发器之间出现过大的延时,消除速度瓶颈。

FPGA/CPLD开发软件中也有一些参数设置,通过修改这些设置,可以提高编译/布局布线后系统速度,但是根据经验这种速度的提高是很有限的,假如按照要求我们需要设计一个可以工作到50MHz的系统,实际布局布线器报告出来的Fmax只有40MHz,此时如果我们使用布局布线器的设置选项最多可以提高到45MHz,这还是运气比较好的情况。而且你必须了解这些选项的含义、使用背景等。

其实在一个设计里影响速度的瓶颈经常只会有几条,我们将延时最大的路径称作关键路径。当设计的运行速度不符合系统设计要求的时候我们可以首先找到不能满足要求的关键路径,按照上述的方法将关键路径上的组合逻辑拆分成多个中间用触发器隔开,这样很容易就可以从根本上提升系统的运行速度了。

有的设计在设计开始就知道那部分电路会产生比较大的组合逻辑,导致速度瓶颈的产生,那么就应该在开始就想好解决办法。比如现在设计需要产生一个32位的加法器,并且要求能够工作在50MHz。根据经验直接用32位加法器肯定是达不到50MHz的要求的,这时我们可以将其分成3个12位计数器来操作,后面的计数器只要将前面计数器结果的高位(进位位)相加就可以了。

下面是原来在宽带接入服务器设计中的流量统计单元中的32位加法器的描述:

----------------------------------------------------------

---- flow count element

----------------------------------------------------------

-----temporary compuTIng 12 bits adder

process(Count_0_en,count_buffer,Len,Carry_0_0,Carry_0_1)

begin

case Count_0_en is

---1st Step addiTIon (10 downto 0) + (10 downto 0)

when "001" => add_12_a_0 <= ('0' & count_buffer(0)(10 downto 0));

add_12_b_0 <= ('0' & Len(10 downto 0));

---2nd Step addiTIon (21 downto 11) + Carry_0_0

when "010" => add_12_a_0 <= ('0' & count_buffer(0)(21 downto 11));

add_12_b_0 <= ("00000000000" & Carry_0_0);

---3rd Step addiTIon (31 downto 22) + Carry_0_1

when "100" => add_12_a_0 <= ("00" & count_buffer(0)(31 downto 22));

add_12_b_0 <= ("00000000000" & Carry_0_1);

when others => add_12_a_0 <=(others=>’X’);

add_12_b_0 <=(others=>’X’);

end case;

end process;

------12 bits adder

add_12_result_0 <= add_12_a_0 + add_12_b_0;

------Bytes Count

process(RST,CLK_25MHz,IO,OE_bar,data_sel,Count_0_en)

begin

if(RST = '1')then -----system Reset

count_buffer(0) <= (others => '0');

Carry_0_0 <= '0';

Carry_0_1 <= '0';

Carry_0_2 <= '0';

elsif(CLK_25MHz'event and CLK_25MHz = '0')then

if(OE_bar = '0' and data_sel = '0')then

count_buffer(0) <= IO;

Carry_0_2 <= '0';

else

case Count_0_en is

---1st Step addition (10 downto 0) + (10 downto 0)

when "001" => count_buffer(0)(10 downto 0) <= add_12_result_0(10 downto 0);

Carry_0_0 <= add_12_result_0(11);--first step carry

---2nd Step addition (21 downto 11) + Carry_0_0

when "010" => count_buffer(0)(21 downto 11) <= add_12_result_0(10 downto 0);

Carry_0_1 <= add_12_result_0(11);--Second step carry

---3rd Step addition (31 downto 22) + Carry_0_1

when "100" => count_buffer(0)(31 downto 22) <= add_12_result_0(9 downto 0);

Carry_0_2 <= add_12_result_0(10);--Third step carry

when others => Carry_0_2 <= '0';

end case;

end if;

end if;

end process;

- 数字电路中显示译码器设计的分析与研究(07-12)

- 数字电路设计中部分常见问题解析(01-15)

- 音频专家潘昶:如何进行数码播放器的开发和评估?(02-18)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 数字电路中Multisim10单片机的应用(08-16)

- 步进电机数控解决方案(02-18)