大唐电信FPGA/CPLD数字电路设计经验分享(3)

注意:当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己。

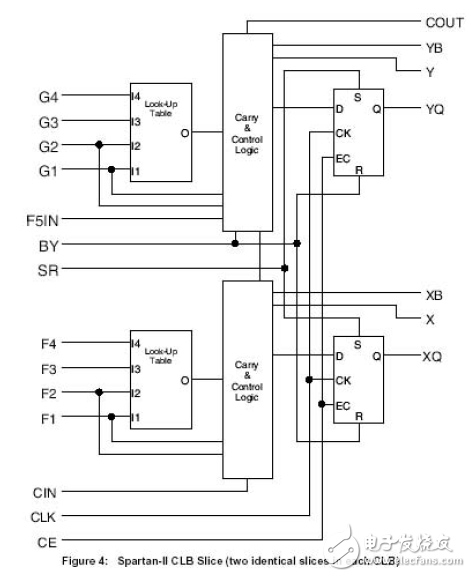

需要说明的是在FPGA/CPLD内部结构是一种标准的宏单元,下图是Xilinx公司的Spartans II系列器件的一个标准宏单元。虽然不同的厂家的芯片宏单元的结构不同,但概括而言都是由一些组合逻辑外加一或二个触发器而构成。在实际应用中,当一个模块内的组合逻辑被使用了那么与其对应的触发器也就不能用了;同样如果触发器单元被用了那么组合逻辑单元也就废了。这就是有时候(特别是使用CPLD)虽然设计使用的资源并不多但布局布线器却报告资源不够使用的原因。

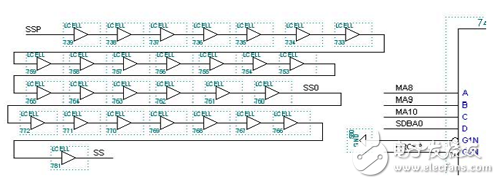

现面的一个例子是前一段时间我在公司遇到的一个设计。设计使用Altera公司的EPM7256型号的CPLD。该设计实际使用的寄存器资源只有109个,占整个器件资源的42%。可是该设计使用了如下图所示的延时方法来做处理器接口的时序:

现面的一个例子是前一段时间我在公司遇到的一个设计。设计使用Altera公司的EPM7256型号的CPLD。该设计实际使用的寄存器资源只有109个,占整个器件资源的42%。可是该设计使用了如下图所示的延时方法来做处理器接口的时序:

在该电路的设计中使用了大量的LCELL来产生100多纳秒的延时,这样做的后果是虽然整个电路的触发器资源只使用了42%,可是用MaxplusII进行布局布线已经不能够通过了。而且我怀疑经过这么多逻辑的延时后所产生的信号还能保持原来的性能不。

当需要对某一信号作一段延时时,初学者往往在此信号后串接一些非门或其它门电路,此方法在分离电路中是可行的。但在FPGA中,开发软件在综合设计时会将这些门当作冗余逻辑去掉,达不到延时的效果。用ALTERA公司的MaxplusII开发FPGA时,可以通过插入一些LCELL原语来产生一定的延时,但这样形成的延时在FPGA芯片中并不稳定,会随温度等外部环境的改变而改变,因此并不提倡这样做。在此,可以用高频时钟来驱动一移位寄存器,待延时信号作数据输入,按所需延时正确设置移位寄存器的级数,移位寄存器的输出即为延时后的信号。此方法产生的延时信号与原信号比有误差,误差大小由高频时钟的周期来决定。对于数据信号的延时,在输出端用数据时钟对延时后信号重新采样,就可以消除误差。

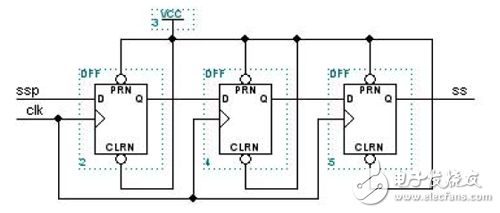

对于这样大的延时我建议的实现方法是采用时钟锁存来产生延时的方法,我们知道当一个信号用时钟锁存一次,将会占用一个触发器资源,信号会向后推移一个时钟周期;该同事的设计里CPLD芯片正好连接有32MHz的时钟,那么每用时钟锁存一次ssp信号就会推移31ns,这样只需多使用3个触发器资源就可以达到目的了。电路图和仿真波形如下图所示:当然这样做对原来信号高低电平的宽度会稍有改变,但只要是在与其接口的芯片的容许范围之内就不会影响到功能的实现。

用于延时的电路图

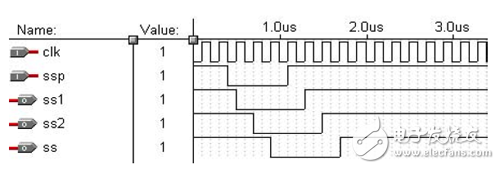

上图仿真波形

2.3 如何提高系统的运行速度

同步电路的速度是指同步时钟的速度。同步时钟愈快,电路处理数据的时间间隔越短,电路在单位时间处理的数据量就愈大.

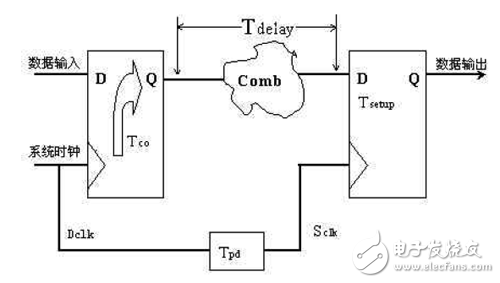

我们先来看一看同步电路中数据传递的一个基本模型,如下图:

(Tco是触发器时钟到数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间)

假设数据已经被时钟的上升沿打入D触发器,那么数据到达第一个触发器的Q端需要Tco,再经过组合逻辑的延时Tdelay到达的第二个触发器的D端,要想时钟能在第二个触发器再次被稳定的锁入触发器,则时钟的延迟不能晚于Tco+Tdelay+Tsetup,(我们可以回顾一下前面讲过的建立和保持时间的概念,就可以理解为什么公式最后要加上一个Tdelay) 由以上分析可知:最小时钟周期:T=Tco+Tdelay+Tsetup 最快时钟频率 F= 1/T PLD开发软件也正是通过这个公式来计算系统运行速度Fmax。

注:在这个逻辑图中有个参数:Tpd ,即时钟的延时参数,我们在刚才做时间分析的时候,没有提这个参数,(如果使用PLD的全局时钟型号,Tpd可以为0,如果是普通时钟,则不为0)。所以如果考虑到时钟的延时,精确的公式应该是T=Tco+Tdelay+Tsetup-Tpd。当然以上全部分析的都是器件内部的运行速度,如果考虑芯片I/O管脚延时对系统速度的影响,那么还需要加一些修正。

由于Tco、Tsetup是由具体的器件和工艺决定的,我们设计电路时只可以改变Tdelay。所以缩短触发器间组合逻辑的延时是提高同步电路速度的关键。由于一般同步电路都不止一级锁存(如图3),而要使电路稳定工作,时钟周期必须满足最大延时要求,缩短最长延时路径,才可提高电路的

- 数字电路中显示译码器设计的分析与研究(07-12)

- 数字电路设计中部分常见问题解析(01-15)

- 音频专家潘昶:如何进行数码播放器的开发和评估?(02-18)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 数字电路中Multisim10单片机的应用(08-16)

- 步进电机数控解决方案(02-18)