在FPGA开发中尽量避免全局复位的使用?(2)

时间:02-11

来源:网络整理

点击:

在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。如果所有的触发器都使用这一全局复位信号,则GSR信号将形成一个高扇出的网络(有兴趣的朋友可以在综合工具中查看)。虽然在启动顺序中,它可以与一个用户自定义的时钟进行同步,但是想让它与设计中的所有时钟信号进行同步是不可能的;比如,一个Xilinx FPGA中可能含有多个DLL/DCM/PLL时钟处理模块,每个模块又可以产生多个时钟信号,在各个模块内部进行时钟信号的同步是可行的,然而想让所有时钟信号同步是完全不可行的——从DCM的分布上就可以看出来:中间相隔的长距离布线对高频时钟信号的延时显著增大,进行同步自然无法做到。于是,在时钟信号频率越来越高的情况下,全局复位信号便开始成为时序关键。解释如下:

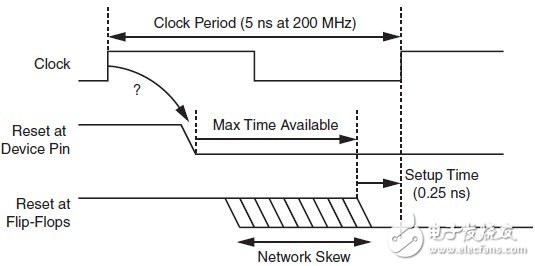

图1被两个时钟信号的边沿截断的复位信号的时序图

图1 给出了被两个时钟信号的边沿截断的复位信号的时序图,第一行是时钟信号,第二行是器件复位管脚上的信号,第三行是到达触发器复位端的复位信号。为了使触发器进行有效的复位,在有效的时钟边沿到来之前,复位信号应该被保持至少一个建立时间(时钟信号的简历时间)。可以看出,时钟信号的频率越高,用来分配复位信号的可用时间就越少。而且考虑到全局复位信号往往是高扇出的的网络,想在这个庞大的网络中满足苛刻的时序要求是非常困难的。在经常使用的异步复位的设计中,更没有办法来保证所有的触发器都可以在同一个时钟边沿被释放,即使存在用来分配复位信号的可用时间。这一点从图2中可以看出。

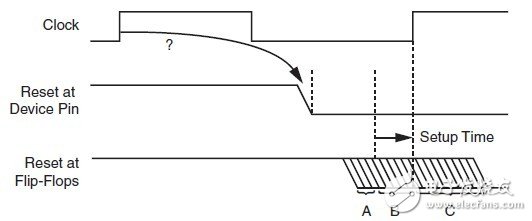

图2 异步设计中复位信号的时序图

图2给出了异步设计中复位信号的时序图。可以看出,在A时刻产生的复位信号,将在第一个时钟信号的有效边沿产生,而在C时刻产生的复位信号将在第二个有效的时钟信号边沿产生。在B时刻,触发器很难有效定义哪一个复位信号是有效的,这将导致亚稳态的产生。随着时钟信号频率的增高和器件规模增大带来的潜在的时钟偏移,在同一个时钟边沿对所有的触发器进行是否已经几乎是不可能的了。图3显示了高时钟频率下的复位时序图。

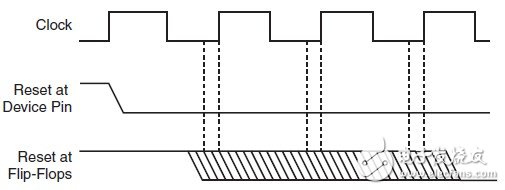

图3 高时钟频率下的复位时序

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)