基于FPGA的交流电机驱动器的电流控制器3

仿真和算法改进步骤

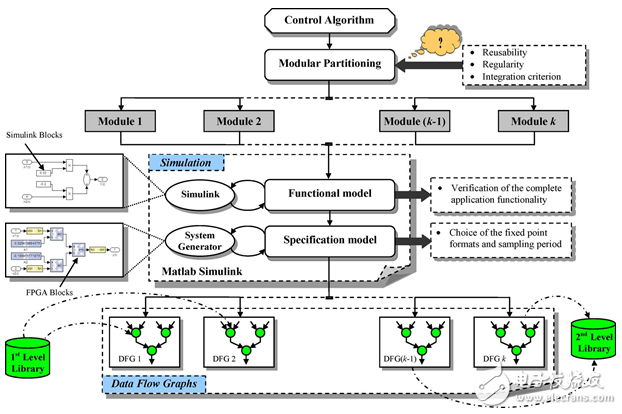

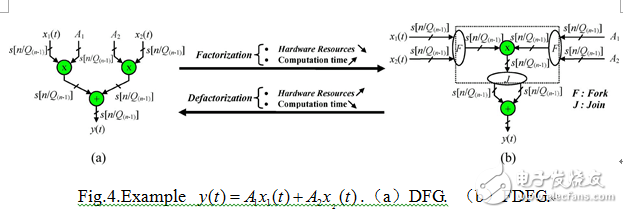

正如之前所提到,仿真步骤在Matlab-simulink软件环境中已经演示过。它的目标是: 改变完整的控制系统的功能;根据控制系统的缺陷所需,找到每个控制变量合适的采样周期和定点格式改进。在利用仿真连续时间模块情况下,功能模块的发展能够促使这些功能成功地改变。然而,每个组合数字算法的参数化是在研究采样周期和定点格式的影响下得到的。注意到这一点,每个定点格式的选择都源于可适应的方法[30],[31]。在此等级下,仿真是在使用系统生成工具箱的数字定点专用模型的发展下实现的[32]。然而,对于每个提出的第二等级的模块来说,提出了数据流曲线图这一概念(DFG)。DFG是算法的图形再现,它包括不定时的规范,由点和边沿组成。每个点表示一个简单的算法操作,或一个简单的数学或逻辑功能,每个边沿对应数据转换。例如,如图4(a)所示,第二算法等级的DFG图展示了下式功能:(1)正如关联图DFG所示,在并行模式中可以完成两种应用,但是附加的应用依赖于两种应用的已得结果,并且只有在两种应用取得结果的条件下才能实现。因此,DFG图明确地表示数据依赖关系性和算法的潜在并行性。图3表示了提出的不同的步骤。值得注意的是,到目前为止,关于目标器件的抉择还没能得到,因为模块分离和定点改进也适用于DSP控制器[33]。

步骤最优化

步骤最优化是建立在A3技术的基础之上的[28],此方法的目的是,若进行基于FPGA设计,那么它是在满足空间和时间限制下达到给出算法的硬件结构最优化。在每个DFG图中,某些操作使用数次。如果某些操作使用了n遍,那么A3将进行因式分解处理但仍然适用于此操作,只不过它是仅使用了m遍,而m<n,大部分时候m的值都为1。在给出的操作当硬件支持时,操作必须能被识别。A3技术一般应用于硬件资源消耗贪婪的操作器如倍增器。DFG因式分解的结果是把数据流曲线图进行分解(FDFG)。图4(b)所示为一个倍增器FDFG实例。从图上可以注意到,分解过程虽减少了硬件资源的消耗,但却增加了计算时间。然而,最后用来硬件结构的设计图当然是介于硬件资源消耗和计算时间中间的适当水平。对于电子系统控制器,被用过的采样周期远大于计算延时,在此情况下,首要任务是减少硬件资源消耗。

模块化硬件结构设计

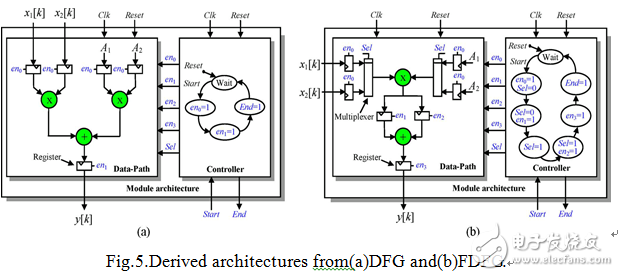

对于库中每个模块,都需要定义一个数据通道和一个控制装置。结构中的数据通道可以用来代替最终图形中的节点所对应的操作器以及边沿对应的操作器之间的数据总线。数据总线转换由控制装置控制管理,它简单地可以被称为有限状态机(FSM)。图5(a)和图5(b)结构分别对应图4中DFG和FDFG。值得注意的是,已获得的数据通道其实是对应图形的拟拷贝,此外,因式分解的结构较未能因式分解的结构的潜力大很多。

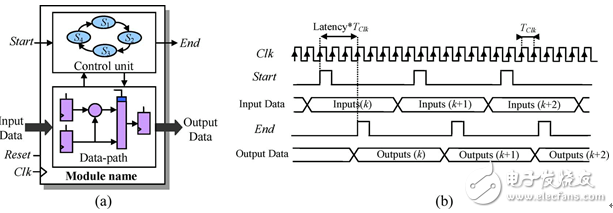

Fig.6.(a)Generic module architecture.(b)TIming diagram of the module. 至于第三等级模块的硬件结构的发展,可以这么说它是利用库中第一、二等级模块中的块进行运作的。因此,数据通道是第一、二等级模块组合的实例化,它连接着数据总线。在这个程度上来说,第二等级模块的结构可以被认为是粗晶粒操作器。对于这种操作器,一个A3的因式分解过程只能应用一次。这么说,如果控制算法包括两个PI控制器,那么设计只能任意选择其中唯一一次因式分解的PI控制器。第二等级的模块容易操作把控,这只取决于它们的Start和End信号。对于这些模块的协调是通过全局控制装置在明确的界定时间点发出信号激活本地控制装置而完成的,这一过程如图7所示。全局控制装置当然也是在由"Start"脉冲信号激活,然后在输出数据完成后产生的"End"脉冲信号中结束的。对于这种结构,第三等级模块也同样用同样的方式在上一等级模块结构中运作。然而,每个等级模块的结构可以通过结构性方法VHDL语言进行编码。

Fig.6.(a)Generic module architecture.(b)TIming diagram of the module. 至于第三等级模块的硬件结构的发展,可以这么说它是利用库中第一、二等级模块中的块进行运作的。因此,数据通道是第一、二等级模块组合的实例化,它连接着数据总线。在这个程度上来说,第二等级模块的结构可以被认为是粗晶粒操作器。对于这种操作器,一个A3的因式分解过程只能应用一次。这么说,如果控制算法包括两个PI控制器,那么设计只能任意选择其中唯一一次因式分解的PI控制器。第二等级的模块容易操作把控,这只取决于它们的Start和End信号。对于这些模块的协调是通过全局控制装置在明确的界定时间点发出信号激活本地控制装置而完成的,这一过程如图7所示。全局控制装置当然也是在由"Start"脉冲信号激活,然后在输出数据完成后产生的"End"脉冲信号中结束的。对于这种结构,第三等级模块也同样用同样的方式在上一等级模块结构中运作。然而,每个等级模块的结构可以通过结构性方法VHDL语言进行编码。

- 基于FPGA的交流电机驱动器的电流控制器1(02-11)

- 基于FPGA的交流电机驱动器的电流控制器2(02-11)

- 基于FPGA的交流电机驱动器的电流控制器4(02-11)