基于FPGA的交流电机驱动器的电流控制器3

时间:02-11

来源:网络整理

点击:

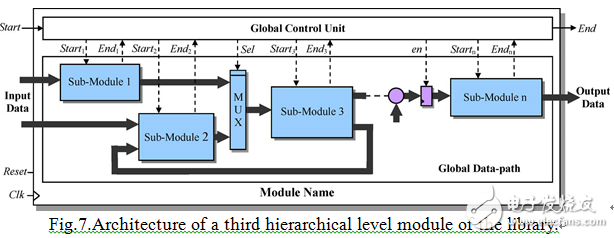

Fig.6.(a)Generic module architecture.(b)TIming diagram of the module. 至于第三等级模块的硬件结构的发展,可以这么说它是利用库中第一、二等级模块中的块进行运作的。因此,数据通道是第一、二等级模块组合的实例化,它连接着数据总线。在这个程度上来说,第二等级模块的结构可以被认为是粗晶粒操作器。对于这种操作器,一个A3的因式分解过程只能应用一次。这么说,如果控制算法包括两个PI控制器,那么设计只能任意选择其中唯一一次因式分解的PI控制器。第二等级的模块容易操作把控,这只取决于它们的Start和End信号。对于这些模块的协调是通过全局控制装置在明确的界定时间点发出信号激活本地控制装置而完成的,这一过程如图7所示。全局控制装置当然也是在由"Start"脉冲信号激活,然后在输出数据完成后产生的"End"脉冲信号中结束的。对于这种结构,第三等级模块也同样用同样的方式在上一等级模块结构中运作。然而,每个等级模块的结构可以通过结构性方法VHDL语言进行编码。

验证设计结构

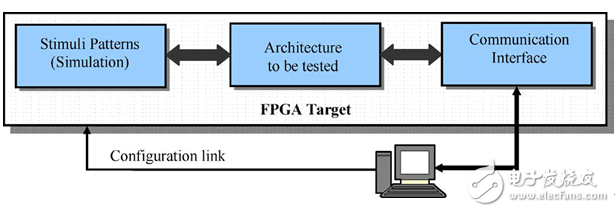

验证的第一步是使用Modelsim和Maltab软件工具一起进行过程运作仿真。这一步骤允许通过编写VHDL修改设计结构中的良性功能,同时可以经过一系列实验平台输入波形进行测试。第二验证步骤是在系统级程度上通过硬件在回路运行步骤完成的,这个过程的目的在于确保第一次实验担保,它通过在测试结构中进行硬件实时完成的,如图8所示,它主要包括三个模块。第一个是产生促进模式,并保存在FPGA存储模块中。这些促进模式直接来源于模拟阶段,能够与模拟系统进行进一步比较。第二个模块是被用来测试的结构,第三个模块是一个连接FPGA和PC主机的通信接口模块。此结构的计算输出应当集中进行测试并通过通信接口送往PC主机,此目的是为了与在Matlab环境下仿真的结果进行比较。一旦这个测试结果被验证成功,那么次设计的结构将可以应用于实际。

- 基于FPGA的交流电机驱动器的电流控制器1(02-11)

- 基于FPGA的交流电机驱动器的电流控制器2(02-11)

- 基于FPGA的交流电机驱动器的电流控制器4(02-11)