一种基于FPGA的PXA270外设时序转换接口设计

时间:02-11

来源:网络整理

点击:

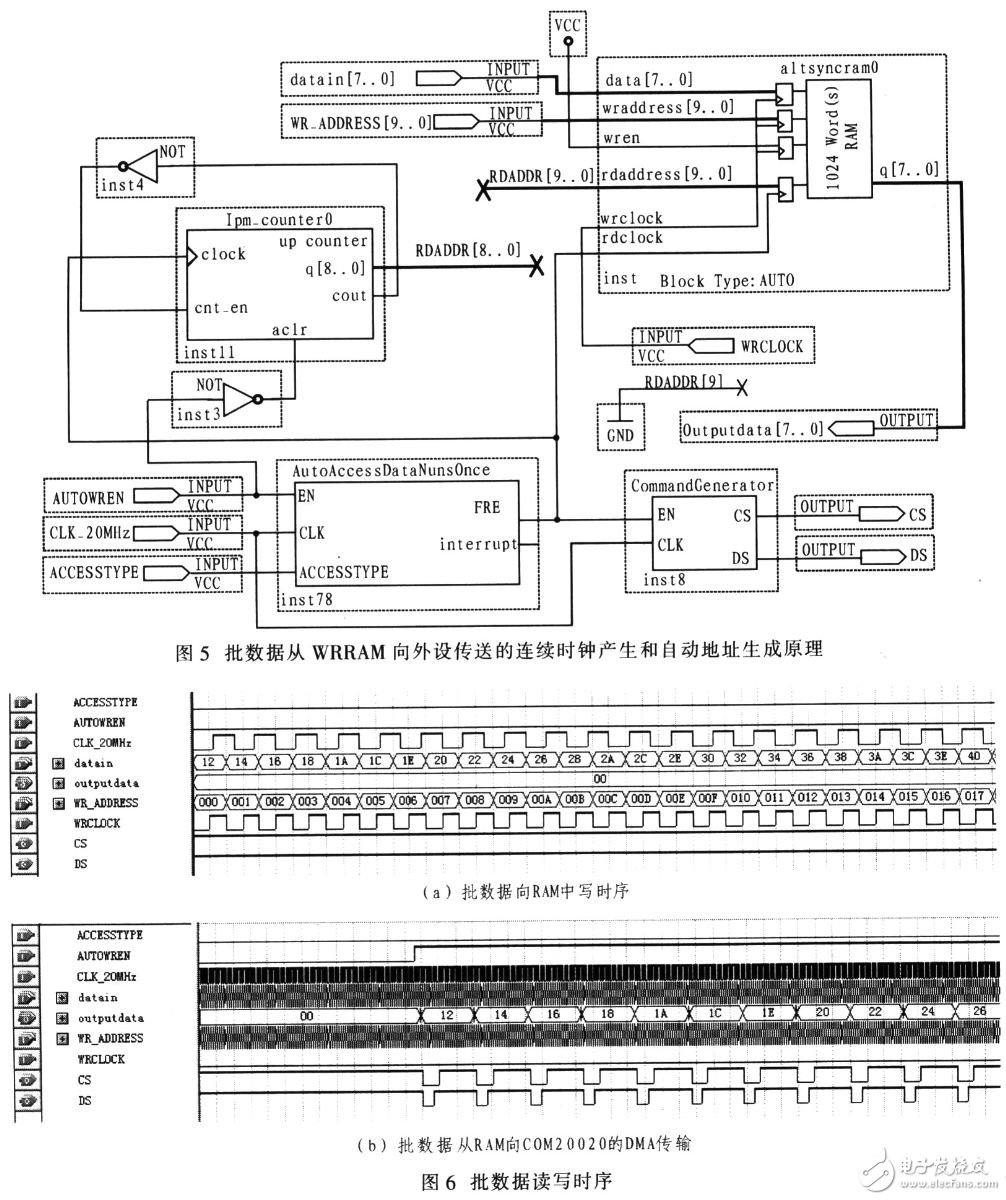

图6为一次批数据向RAM中写,而后启动DMA传输,将数据从RAM送至COM20020的时序仿真。在WRCLOCK上升沿时,RAM将datain总线上的数据存储到WR_AD-DRESS所指向的字节地址空间,WRCLOCK信号是由PXA270的WE信号与分配给RAM的片选信号(高电平有效)相与而得。对RAM进行模拟写时必须确保AUTOWREN无效(低电平);在检验数据DMA传输的RAM输出环节,WRCLOCK应不再出现上升沿信号,以防RAM同时读写造成输出不定值。此外,每个数据从outputdata端口输出时,CS、DS在一定延时后(1个CLK时钟周期)给时序产生留足够时间。需说明:COM20020内部有2 K字节的RAM空间,用于存放待发送或已接收的数据包,在向RAM中写数据包前,指定该数据包的存放位置,然后将COM20020中的指针自动移动位置 1,则只需连续的向该RAM中写数据,而不必给出地址信号。 3.3 对外设指定寄存器操作 对外设指定寄存器操作比批数据传送实现简单,只需将操作次数降为1次,并对 COM20020的A2~A0提供相应的地址即可。指定寄存器操作将数据存储在RAM的高512字节空间,并且只占用其中低8个字节,在PXA270编程时,需确保PXA270送入RAM的地址与命令寄存器中的RAM存储地址COMMANDBYTE[2..0]相对应。

4 结论 本设计解决ARCNET协议专用器件应用于列车通信网络中的时序匹配问题,实现了PXA270处理器与COM20020的时序转换。此外,对扩展其他总线访问类型提供了参考框架,可通过修改CommandGenerator中COM20020时序,实现不同外设总线访问类型的扩展;修改 AutoAccessDataNun-sOnce中的ACCESSTYPE,可配置批数据操作的数据种类。

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)