Xilinx可编程逻辑器件设计与开发(基础篇)连载34:Spartan

9.3 ChipScope Pro内核插入器

ChipScope Pro内核插入器的文件后缀名为cdc。在ISE工程中可以创建一个新的cdc程序,也可以在实现流程中激活内核插入器。

注意:使用内核插入器之前,要注意一些工程项目的属性设臵。

(1) 如果采用XST综合工具,将【Keep Hierarchy】属性设置成【Yes】或【Soft】,禁止XST工具对设计的优化,保留原来设计层次,同时也保留了NET网络节点名称。设置方法如下。

选择【Edit】→【Preferences】,打开属性对话框。

选择【Processes】页。

设臵属性显示下拉框为【Advanced】,单击【OK】。

右击【Synthesize】,选择【ProperTIes】选项。

设臵【Keep Hierarchy】属性为【Yes】或【Soft】,单击【OK】。

(2) 正确设置比特流生成选项。

在Project Navigator里,单击【Generate Programming File】右键,选择【ProperTIes】选项。

选择【Startup opTIons】页。

选择【FPGA Start-Up Clock】下拉框,JTAG Clock启动时钟。

接下来,介绍如何在ISE的环境下调用ChipScope的内核插入器(Core Inserter),以及内核插入器的各种参数的含义及其配置方法。

1. 运行ISE 11.1,打开设计的工程项目。

2. 创建CDC文件。在ISE11.1的界面下,有两个创建CDC文件的方法:

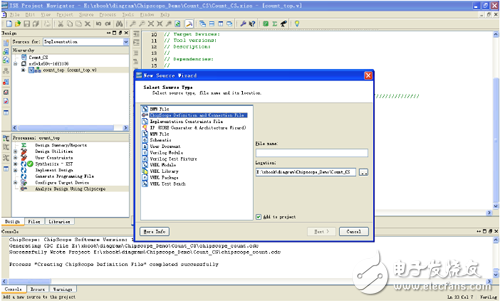

单击选择【Project】→【New Source】,弹出源程序设臵界面,选择【ChipScope DefiniTIon and Connection File】,输入文件名,如图9-28所示。单击【Next】,按照缺省设臵产生和配臵调试内核,直到【Finish】生成.cdc文件。

注意:只有安装了ChipScope Pro 11.1,才可以在ISE 11.1的【New Source】里出现【ChipScope Definition and Connection File】。

图9-28 【New Source Wizard】源程序类型选择界面

选择【Project】→【Add Source】(【Add Copy of Source】),选择已经存在的.cdc文件。

3. ChipScope内核插入器的属性和参数设置。

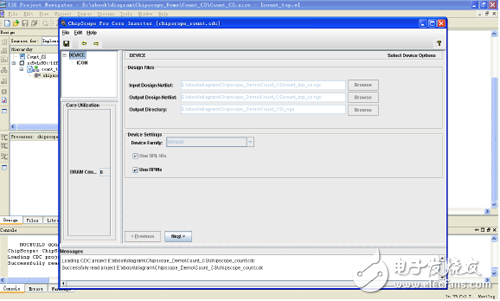

(1) 在【Sources in Project】窗口中,双击cdc文件。弹出的内核插入器界面如图9-29所示,设置Chipscope Pro的参数。

图9-29 内核插入器用户界面

菜单栏中的菜单项及其功能有:

【File】菜单:包含常见的文件操作命令,如【Open Project】、【Save】、【Save As】。【Refresh Netlist】用于手动更新网表。

【Edit】菜单:包含创建新的集成逻辑分析单元【New ILA Unit】,或者创建新的ATC2单元【New ATC2 Unit】,删除单元【Remove Unit】,以及参数设臵【Preferences】等命令。

【Insert】菜单:包含【Insert Core.】命令,当设臵ILA Core的各项参数后,可以利用这个命令把集成逻辑分析仪的网表插入到原设计的网表中。

【Design Files】设计文件选项组,有如下几个选项:

指定输入设计的网表

单击【Browse】,选择输入设计所在的目录

修改输出设计网表和输出目录(如果核插入器在ISE里激活,那么输入网表和输出网表、目录、器件型号等参数自动填入,在这钟情况下,这些参数只能在ISE工程属性中修改,不在核插入器里修改。)

工程参数

【Device Setting】器件设置选项组:

【Device Family】:选择目标FPGA器件家族,内核生成器会生成针对该器件优化的ICON和捕获内核。

【Use SRL16s】:用来控制是否用SRL16和SRL16E逻辑生成内核,如果不选择该选项,将会用触发器和多路选择器来代替,影响生成核的大小和性能。缺省设臵为使能。

【Use RPMs 】:用来控制是否用相关布局宏(RPMs)生成一个独立的内核,该复选框能阻止布局布线器对区域内放臵ChipScope Pro内核的逻辑进行布局优化。如果设计中占用了大部分的逻辑资源,这些布局限制有可能不被满足。

【Core Utilization】选项组:内核生成器的左边是内核资源利用显示窗口,列出插入设计网表中的ChipScope核资源利用情况,包括查找表(LUT), 触发器 (FF)和块RAM (BRAM)。

注意:只有Spartan-3、Spartan-3E、Spartan-3A、Spartan-3A DSP和Virtex-4器件家族显示ChipScope核资源利用特性。

(2) ICON核配置选项设置。在图9-29中单击【Next】,弹出ICON核配置选项设置界面,如图9-30所示。

图9-30 ICON核配置选项界面

【Boundary Scan Chain】下拉选择框:边界扫描链,分析仪可以通过USER1、USER2、USER3或USER4边界扫描链与ChipScope内核通信。(Spartan-3、Spartan-3E、Spartan-3A或Spartan-3A DSP器件不支持该选项。)

可以禁止BUFG插入。

打开【Edit】菜单→【Preferences】属性,弹出【Edit

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)