Xilinx可编程逻辑器件设计与开发(基础篇)连载16:Spartan

Spartan-6器件具有2或4个专用嵌入式多端口存储器控制器模块(MCB),实现了到4个常见存储器标准的简单连接:DDR3、DDR2、DDR 和LPDDR(移动DDR)。

Spartan-6器件为专用MCB模块提供了高达800Mbit/s 的数据速率,并且其存储器接口性能是上一代和竞争低成本FPGA 解决方案的2 倍。使用专用存储器控制器还有很多功耗节省优势,特别是它支持低功耗DDR(LPDDR)标准。主要特点如下。

DDR、DDR2、DDR3和LPDDR支持。

数据速率高达800Mbit/s(12.8Gbit/s 峰值带宽)。

内部32 bit、64 bit或128 bit数据接口为MCB提供了简单而又可靠的接口。

带有独立FIFO的多端口总线结构减少了设计时序问题。

存储器接口设计的可预测时序。

软件向导介绍了整个工艺。

2.1.8 GTP模块

Spartan-6 LXT FPGA可提供多达8个3.125Gbit/s GTP收发器和一个集成的PCI Express兼容硬核。两者都源于成熟可靠的Virtex 技术,为串行连接提供了业界最低风险和最低成本的解决方案。

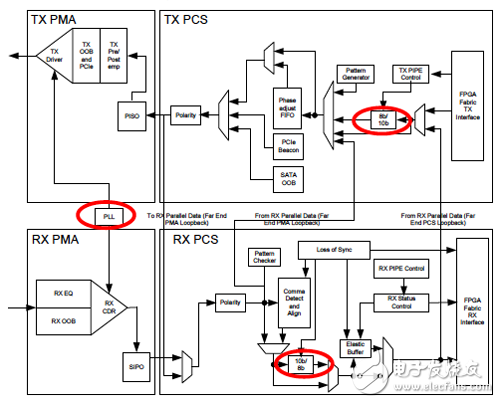

图2-52所示为Spartan-6 GTP框图,GTP收发器模块包含一个发射器和接收器对,能够在622Mbit/s至3.125Gbit/s的数据速率下工作,其主要特点如下。

图2-52 Spartan-6 GTP 框图

多达8 个收发器。

性能高达3.125Gbit/s。

高速接口:SATA、Aurora、1G 以太网、PCI Express、OBSAI、CPRI、EPON、GPON、Display Port 和XAUI。

低功耗:在3.125Gbit/s 下,功耗低于150mW(典型值)。

内部的电流模式逻辑(CML)驱动器和缓存器提供用户可配置的终端、电压摆幅和耦合。

可编程的发送预加重和接收均衡功能。

多种传输工业标准。

614Mbit/s 到810Mbit/s。

1.22Gbit/s 到1.62Gbit/s。

2.45Gbit/s 到3.125Gbit/s。

集成了可选的8b/10b、逗号校准、信道绑定以及时钟校正模块。

固定延时模式。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)