Xilinx可编程逻辑器件设计与开发(基础篇)连载40:Spartan

2. 设置禁止I/O 分配。

最大化【Package Pins】,如图10-45 所示, 和按钮配合,完成对器件引脚的排序,如图中我们将所有VREF 引脚排在一起,选中所有VREF 引脚,右键功能选择【Set Prohibit】,禁止所有VREF 引脚的分配。

图10-45 禁止引脚分配

三、 定义兼容器件

在FPGA 设计开发阶段,PlanAhead 允许设计者定义互相兼容的芯片,这种方式可以将一个I/O约束应用于多个FPGA。

在【Device】或者【Package】窗口,在右键弹出菜单中选择【Make Part CompaTIble…】,选择互相兼容的器件。如图10-46。

图10-46 指定兼容器件

四、 导入、分析I/O端口列表

PlanAhead能够导入多种不同格式的文件用于I/O引脚的规划。在产生综合网表之前,可以导入CSV、UCF和RTL格式的文件进行I/O引脚的分析和分配。但需要注意的是,使用这种早期I/O引脚规划方法的时候,因为没有综合网表,I/O分配工具和DRC校验工具不清楚设计中的时钟和各时钟之间的关系,也不清楚高速逻辑的具体情况,所以其分析并不完整。如果可能的话,导入综合网表后,再进行I/O分配。

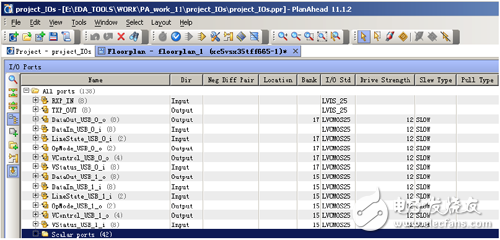

运行命令【File】→【Import I/O Port…】→【From CSV…】导入CSV格式文件,CSV文件目录是PlanAhead_Tutorial\Sources\IO_port_import.csv。最大化【I/O Ports】窗口,如图10-47所示,可以看到默认情况下所有Ports的分布。单击【I/O Ports】窗口旁边的按钮,观察端口排列的变化。图中显示了各个端口的常用属性。

图10-47 【I/O Ports】窗口

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)